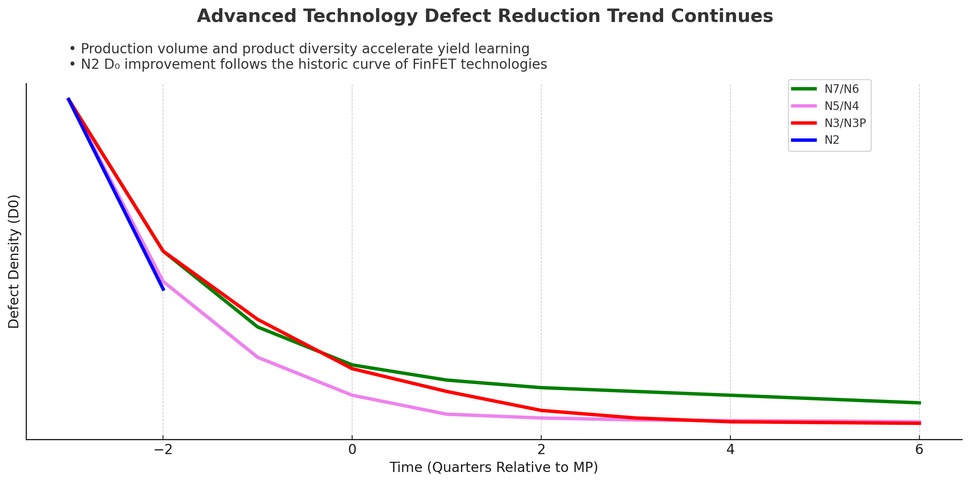

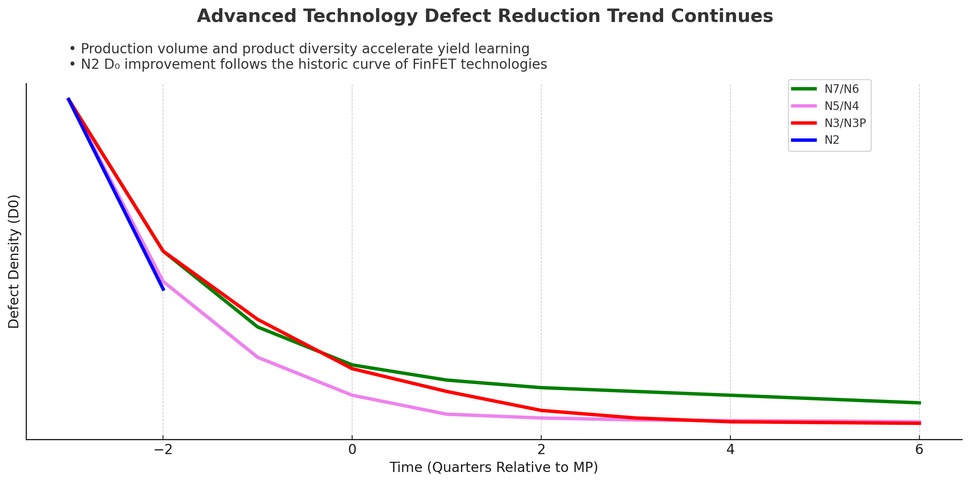

TSMC kündigte kürzlich bei einem nordamerikanischen Technologie -Seminar die Defektdichte (D0) seiner N2 (2NM) -Prozessechnologie im Vergleich zu seinen Vorgängerprozessen im selben Stadium an.Nach Angaben des Unternehmens ist die Mangeldichte des N2 -Prozesses niedriger als die von N3 (3nm), N5 (5nm) und N7 (7 nm) Herstellungsknoten.Darüber hinaus zeigt die Folie, dass der N2 -Prozess von TSMC nach wie vor zwei Viertel von der Massenproduktion entfernt ist, was bedeutet, dass TSMC bis zum Ende des vierten Quartals von 2025 wie erwartet 2nm -Chips produzieren wird.

Obwohl der N2 -Prozess von TSMC die erste Prozesstechnologie des Unternehmens für Nanoblatttransistoren des Full Gate Ring (Gate Ring) ist, ist die Defektdichte dieses Knotens niedriger als der Prozess der vorherigen Generation in derselben Phase, zwei Viertel vor der Massenproduktion (MP).Die Vorgängergenerationsprozesse- N3/N3P, N5/N4 und N7/N6- Alle verwendeten reifen Flossen-Feldeffekttransistoren (Funkeln).Obwohl N2 der erste Knoten von TSMC für die Übernahme von GAA -Nanoblatttransistoren ist, ist die Reduktion der Defektdichte größer als der Prozess der vorherigen Generation, bevor er in den Meilenstein der Massenproduktion (HVM) eintritt.

Dieses Diagramm zeigt die Variation der Defektdichte im Laufe der Zeit von drei Vierteln vor der Massenproduktion bis zu sechs Vierteln nach der Massenproduktion.Unter allen angezeigten Knoten - N7/N6 (grün), n5/n4 (lila), n3/n3p (rot) und n2 (blau) - nimmt mit zunehmender Ausbeute signifikant ab, aber die Abnahmerate variiert abhängig von der Komplexität der Knoten.Es ist erwähnenswert, dass N5/N4 am aktivsten bei der Reduzierung von frühen Defekten ist, während die Ertragsverbesserung von N7/N6 relativ sanft ist.Der anfängliche Defektniveau der N2 -Kurve ist höher als der von N5/N4, nimmt jedoch stark ab, was sehr nahe an der Defektreduzierungstrajektorie von N3/N3p liegt.

Die Folie betont, dass Ertrags- und Produktvielfalt wichtige Antriebsfaktoren für die Beschleunigung der Fehlermangelverbesserung bleiben.Eine größere Produktion und diversifizierte Produkte unter Verwendung desselben Prozesses können die Defektdichte identifizieren und korrigieren und Probleme schneller ergeben, sodass TSMC die Defekt -Lernzyklen optimieren kann.TSMC erklärte, dass seine N2-Herstellungstechnologie mehr neue Chips erhalten hat als die Vorgängertechnologie (da TSMC nun N2-Chips für Smartphones und Hochleistungs-Computing (HPC) -Kunden (HPC) in Gefahr produziert, und die Kurve der Defektdichte wird im Grunde genommen bestätigt.

In Anbetracht der Risikofaktoren, die durch die Einführung einer neuen Transistorarchitektur verursacht werden, ist es besonders wichtig, dass die Defektsreduzierungsrate von N2 mit früheren FINFET -basierten Knoten übereinstimmt.Dies weist darauf hin, dass TSMC das Expertise für Prozesslernen und Defektmanagement erfolgreich auf die neue Gaafet -Ära übertragen hat, ohne auf bedeutende Rückschläge zu stoßen.

RFQs/Bestellung (0)

RFQs/Bestellung (0)

RFQs/Bestellung (0)

RFQs/Bestellung (0)