#### MAX17559

# 60V, Dual-Output, Synchronous Step-Down Controller

#### **General Description**

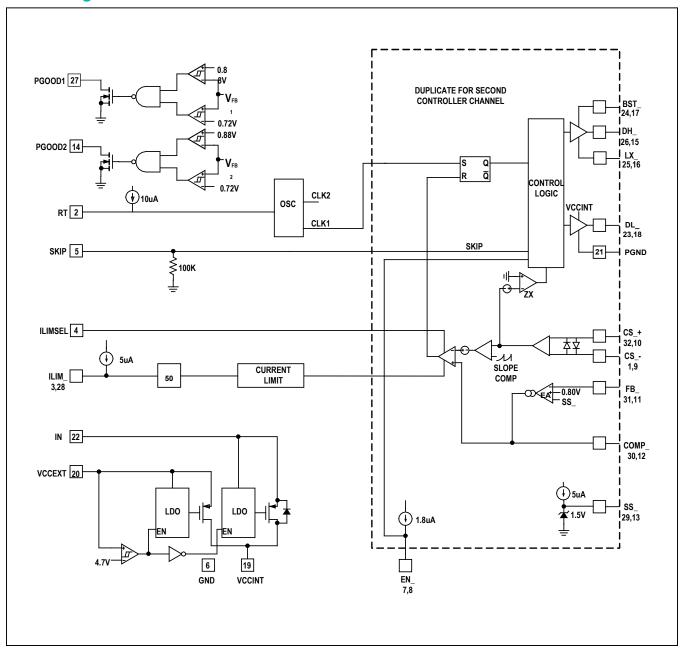

The MAX17559 is a dual-output, synchronous step-down controller that drives nMOSFETs. The device uses a constant-frequency, peak-current-mode architecture.

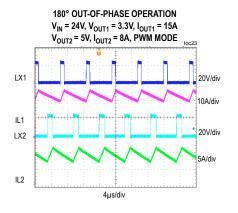

The two outputs can be configured as independent voltage rails. Input capacitor size is minimized by running the two outputs 180° out-of-phase.

The IC supports current sensing using either an external current-sense resistor for accuracy or an inductor DCR for improved system efficiency. Current foldback or latchoff limits MOSFET power dissipation under short-circuit conditions.

The IC provides independent adjustable soft-start/stop for each output and can start up monotonically into a prebiased output. The IC can be configured in either PWM or DCM modes of operation, depending on whether constant-frequency operation or light-load efficiency is desired.

The IC operates over the -40°C to +125°C temperature range and is available in a lead(Pb)-free, 7mm x 7mm, 32-pin TQFP, package.

# **Applications**

- Industrial Power Supplies

- Distributed DC Power Systems

- Motion Control

- Programmable Logic Controllers

- Computerized Numerical Control

#### **Benefits and Features**

- Wide Range of Operation

- Wide 4.5V to 60V Input Voltage Range

- Wide 0.8V to 24V Output Voltage Range

- RSENSE or Inductor DCR Current-Sensing

- · Fixed 180° Out-of-Phase Operation

- Adjustable 100kHz to 2.2MHz Switching Frequency

- Independent Enable and PGOOD

- Available in a Lead(Pb)-Free 7mm x 7mm, 32-Pin TQFP Package

- Enhances Power Efficiency

- Low-Impedance Gate Drives for High Efficiency

- · DCM Operation at Light Loads

- · Auxiliary Bootstrap LDO

- Operates Reliably in Adverse Industrial Environments

- Independent Adjustable Soft-Start/Stop or Tracking

- Current Selectable Foldback or Latchoff Limits MOSFET Heat Dissipation During a Short-Circuit Condition

- Operates Over the -40°C to +125°C Temperature Range

- Output Overvoltage and Overtemperature Protections

Ordering Information appears at end of data sheet.

# **Block Diagram**

# **Absolute Maximum Ratings**

| IN to GND                  | 0.3V to +70V                        | PGOOD_ to GND0.3V to +6                               | V |

|----------------------------|-------------------------------------|-------------------------------------------------------|---|

| CS_+ to GND                | 0.3V to +40V                        | FB_, COMP_, SS_, RT, SKIP, ILIM_, ILIMSEL             |   |

| CS_+ to CS                 | 0.3V to +0.3V                       | 0.3V to (V <sub>CCINT</sub> + 0.3)                    | V |

| LX_, BST_ to PGND          | 0.3V to +70V                        | GND to EP0.3V to +0.3                                 | V |

| BST_ to LX                 | 0.3V to +6V                         | Continuous Power Dissipation at +70°C                 |   |

| BST_ to V <sub>CCINT</sub> |                                     | (Multilayer Board)1666.7m\                            | Ν |

| DH_ to LX                  | 0.3V to (V <sub>BST</sub> + 0.3)V   | Power Deration above +70°C (Multilayer Board)20.8mW/° | С |

| DL_ to PGND                | 0.3V to (V <sub>CCINT</sub> + 0.3)V | Operating Temperature Range40°C to +125°              | С |

| EN_ to GND                 | 0.3V to +6V                         | Maximum Junction Temperature+150°                     | С |

| V <sub>CCINT</sub> to GND  | 0.3V to +6V                         | Storage Temperature Range65°C to +160°                | С |

| V <sub>CCEXT</sub> to GND  | 0.3V to +26V                        | Lead Temperature (soldering, 10s)+300°                | С |

| PGND to GND                | 0.3V to +0.3V                       |                                                       |   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Package Thermal Characteristics(Note 1)

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ )......48°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ )......12°C/W

**Note 1:** Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to <a href="https://www.maximintegrated.com/thermal-tutorial">www.maximintegrated.com/thermal-tutorial</a>.

#### **Electrical Characteristics**

$(V_{IN}$  = 24V, RT = open,  $C_{VCCINT}$  = 4.7 $\mu$ F, EN\_ = open, DH\_, DL\_ = open,  $T_{J}$  = -40 $^{\circ}$ C to +125 $^{\circ}$ C, unless otherwise noted. Typical values are at  $T_{A}$  = +25 $^{\circ}$ C.) (Note 2)

| PARAMETER                      | SYMBOL          | CONDITIONS                                                                                                                            | MIN | TYP | MAX | UNITS       |  |

|--------------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------------|--|

| INPUT SUPPLY                   |                 |                                                                                                                                       |     |     |     |             |  |

| Innut Voltage Denge            | \/.s.           |                                                                                                                                       | 4.5 |     | 60  | V           |  |

| Input Voltage Range            | VIN             | V <sub>CCINT</sub> = V <sub>IN</sub>                                                                                                  | 4.5 |     | 5.5 | \ \ \ \ \ \ |  |

|                                | I <sub>IN</sub> | SKIP = open, LX_ = PGND, BST_ = 5V, EN1 = open, EN2 = GND, $V_{FB1}$ = 0.84V or EN2 = open, EN1 = GND, $V_{FB2}$ = 0.84V              | 0.5 | 1.5 | 2.0 | mA          |  |

| Operating Supply Current (Note |                 | SKIP = open, LX_ = PGND, BST_ = 5V, EN1 = EN2 = open, V <sub>FB1</sub> = V <sub>FB1</sub> = 0.84V                                     | 1   | 2.5 | 3.5 | mA          |  |

| 3)                             |                 | SKIP = $V_{CCINT}$ , LX_ = PGND, BST_ = 5V<br>EN1 = open, EN2 = GND, $V_{FB1}$ = 0.76V or<br>EN2 = open, EN1 = GND, $V_{FB2}$ = 0.76V | 1   | 1.8 | 3.5 |             |  |

|                                |                 | SKIP = $V_{CCINT}$ , LX_ = PGND,BST_ = 5V<br>EN1 = EN2 = open, $V_{FB1}$ = $V_{FB1}$ = 0.76V                                          | 1.5 | 3.2 | 5   |             |  |

| Shutdown Supply Current        |                 | EN1 = EN2 = GND                                                                                                                       |     | 10  | 20  | μА          |  |

# **Electrical Characteristics (continued)**

$(V_{IN}$  = 24V, RT = open,  $C_{VCCINT}$  = 4.7 $\mu$ F, EN\_ = open, DH\_, DL\_ = open, T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                                           | SYMBOL   | CONDITIONS                                                                                                      | MIN                         | TYP  | MAX                        | UNITS        |

|-----------------------------------------------------|----------|-----------------------------------------------------------------------------------------------------------------|-----------------------------|------|----------------------------|--------------|

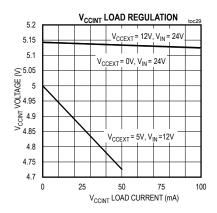

| V <sub>CCINT</sub> REGULATOR                        |          |                                                                                                                 |                             |      |                            |              |

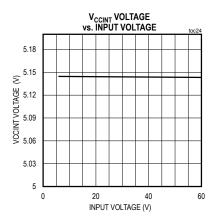

|                                                     |          | 6V < V <sub>IN</sub> < 60V, I <sub>VCCINT</sub> = 1mA                                                           | 4.95                        | 5.1  | 5.25                       |              |

| V <sub>CCINT</sub> Output Voltage                   | VCCINT   | 6V < V <sub>CCEXT</sub> < 24V, I <sub>VCCINT</sub> = 1mA (V <sub>CCINT</sub> supplied from V <sub>CCEXT</sub> ) | 4.95                        | 5.1  | 5.25                       | V            |

| $ m V_{CCINT}$ Load Regulation                      |          | VIN = 12V, I = 0mA to 100mA, VCCEXT = 0V (VCCINT supplied from $VIN$ )                                          | 5                           | 25   | 50                         | mV           |

| *COINT LOSG (VEGUISHOT)                             |          | $V_{VCCEXT}$ = 12V, $I_{VCCINT}$ = 0mA to 100mA ( $V_{CCINT}$ supplied from $V_{CCEXT}$ )                       | 5                           | 25   | 50                         | 111 <b>V</b> |

| V <sub>CCINT</sub> Short-Circuit Output             |          | V <sub>IN</sub> = 8.5V, V <sub>CCEXT</sub> = 0V, V <sub>CCINT</sub> = 4V                                        | 120                         | 250  | 340                        |              |

| Current Current                                     |          | $V_{CCEXT}$ = 8.5V, $V_{CCINT}$ = 4V ( $V_{CCINT}$ supplied from $V_{CCEXT}$ )                                  | 120                         | 250  | 340                        | mA           |

|                                                     |          | V <sub>IN</sub> = 4.5V, load = 75mA, V <sub>CCEXT</sub> = 0                                                     | 50                          | 150  | 420                        |              |

| V <sub>CCINT</sub> Dropout Voltage                  |          | $V_{CCINT}$ supplied from $V_{CCEXT}$ , $V_{IN}$ = 24V, $V_{CCEXT}$ = 4.7V, load = 75mA                         | 50                          | 150  | 420                        | mV           |

| V <sub>CCEXT</sub> Switch Overvoltage               |          | V <sub>CCEXT</sub> rising                                                                                       | 4.55                        | 4.7  | 4.85                       | V            |

| V <sub>CCEXT</sub> Switch Overvoltage<br>Hysteresis |          |                                                                                                                 | 0.2                         | 0.25 | 0.3                        | V            |

| V IIVI O                                            |          | V <sub>CCINT</sub> rising                                                                                       | 4                           | 4.2  | 4.4                        | V            |

| V <sub>CCINT</sub> UVLO                             |          | V <sub>CCINT</sub> falling                                                                                      | 3.5                         | 3.7  | 3.9                        | V            |

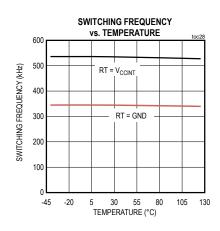

| OSCILLATOR                                          |          |                                                                                                                 |                             |      |                            |              |

|                                                     |          | RT = 62kΩ                                                                                                       | 405                         | 440  | 475                        |              |

| Switching Frequency                                 | $f_{SW}$ | RT = V <sub>CCINT</sub>                                                                                         | 480                         | 535  | 590                        | kHz          |

|                                                     |          | RT = GND                                                                                                        | 325                         | 350  | 375                        |              |

| RT Pullup Current                                   |          | V <sub>RT</sub> = 0.5V                                                                                          | 9.5                         | 10   | 10.5                       | μΑ           |

| Switching Frequency Adjust-<br>able Range           | fsw      | 26.5kΩ < RT < 280kΩ                                                                                             | 100                         |      | 2200                       | kHz          |

| SKIP                                                |          |                                                                                                                 |                             |      |                            |              |

| DCM Mode Setting Range                              |          |                                                                                                                 | 1.25                        |      | V <sub>CCINT</sub><br>-1.6 | V            |

| PWM Mode Setting Range                              |          |                                                                                                                 | V <sub>CCINT</sub><br>- 1.5 |      | V <sub>CCINT</sub>         | V            |

| SKIP Pulldown Resistance                            |          |                                                                                                                 | 70                          | 100  | 130                        | kΩ           |

# **Electrical Characteristics (continued)**

$(V_{IN}$  = 24V, RT = open,  $C_{VCCINT}$  = 4.7 $\mu$ F, EN\_ = open, DH\_, DL\_ = open, T<sub>J</sub> = -40°C to +125°C, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C.) (Note 2)

| PARAMETER                                | SYMBOL                                 | CONDITIONS                                                         | MIN  | TYP  | MAX  | UNITS |

|------------------------------------------|----------------------------------------|--------------------------------------------------------------------|------|------|------|-------|

| GATE DRIVER                              | •                                      |                                                                    |      |      |      |       |

| DH_ to BST_ On-Resistance                |                                        | Sourcing 100mA                                                     | 0.7  | 1.3  | 2.5  | Ω     |

| DH_ to LX_ On-Resistance                 |                                        | Sinking 100mA                                                      | 0.25 | 0.5  | 0.9  | Ω     |

| DL_ to V <sub>CCINT</sub> On-Resistance  |                                        | Sourcing 100mA                                                     | 0.7  | 1.3  | 2.5  | Ω     |

| DL_ to PGND_ On-Resistance               |                                        | Sinking 100mA                                                      | 0.35 | 0.75 | 1.25 | Ω     |

| DH_ Minimum Controlled On-Time           | t <sub>ON_MIN</sub>                    |                                                                    |      | 120  | 155  | ns    |

| DL_ Minimum Controlled Off-Time          | t <sub>OFF_MIN</sub>                   | PWM mode, V <sub>FB</sub> _ = 0.84V                                | 80   | 120  | 160  | ns    |

| Dead Time                                | <b>4</b>                               | DH_ falling to DL_ rising, C <sub>LOAD</sub> = 6nF                 |      | 30   |      | 20    |

| Dead Time                                | t <sub>DT</sub>                        | DL_ falling to DH_ rising, C <sub>LOAD</sub> = 6nF                 |      | 30   |      | ns    |

| DII Transition Time                      |                                        | DH_ rising, C <sub>LOAD</sub> = 6nF                                |      | 25   |      | ns    |

| DH_ Transition Time                      |                                        | DH_ falling, C <sub>LOAD</sub> = 6nF                               |      | 15   |      |       |

| DI Transition Time                       |                                        | DL_ rising, C <sub>LOAD</sub> = 6nF                                |      | 25   |      | 20    |

| DL_ Transition Time                      |                                        | DL_ falling, C <sub>LOAD</sub> = 6nF                               |      | 15   |      | ns    |

| SOFT-START/STOP                          |                                        |                                                                    |      |      |      |       |

| Soft-Start/Stop Current                  | I <sub>SS</sub>                        | V <sub>SS</sub> = 0.5V                                             | 3.5  | 5    | 6.5  | μΑ    |

| ENABLE                                   |                                        |                                                                    |      |      |      |       |

| EN_ Logic-High Threshold                 |                                        | EN_ rising                                                         | 1.2  | 1.25 | 1.3  | V     |

| EN_ Hysteresis                           |                                        |                                                                    |      | 90   |      | mV    |

| EN_Bias Pullup Bias Current              |                                        | V <sub>EN</sub> = 0.5V                                             | 0.9  | 1.8  | 2.7  | μA    |

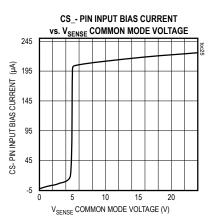

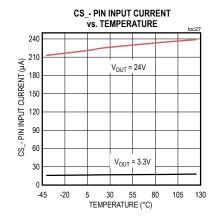

| CURRENT-SENSE AMPLIFIER                  |                                        |                                                                    |      |      |      |       |

| CS_+ , CS Common-Mode<br>Voltage Range   |                                        |                                                                    | 0    |      | 24   | V     |

| CS_+ to CS Input Operating Voltage Range | V <sub>CS+</sub> -<br>V <sub>CS-</sub> | 0 < V <sub>CS-</sub> < 24V                                         | -100 |      | +100 | mV    |

| Current-Sense Amplifier Gain             | G <sub>CS</sub>                        |                                                                    | 12   | 13.3 | 14.5 | V/V   |

| CS+_ Input Bias Current                  |                                        | 0 < V <sub>CS-</sub> < 24V, T <sub>A</sub> = T <sub>J</sub> = 25°C |      | 0.01 | 1    | μΑ    |

| CS Input Bias Current                    |                                        | V <sub>CS+</sub> = V <sub>CS-</sub> = 1.2V or 24V                  | 5    |      | 600  | μA    |

# **Electrical Characteristics (continued)**

$(V_{IN} = 24V, RT = open, C_{VCCINT} = 4.7\mu F, EN_ = open, DH_, DL_ = open, T_J = -40^{\circ}C$  to +125°C, unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 2)

| PARAMETER                                                 | SYMBOL                  | CONDITIONS                                                       | MIN   | TYP  | MAX   | UNITS |  |  |

|-----------------------------------------------------------|-------------------------|------------------------------------------------------------------|-------|------|-------|-------|--|--|

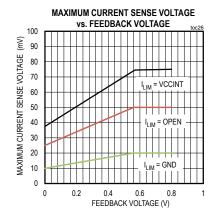

| CURRENT LIMIT                                             |                         |                                                                  |       |      |       |       |  |  |

| ILIM_ reference current                                   |                         |                                                                  | 4.5   | 5    | 5.5   | μA    |  |  |

| Adjustable Cycle-by-Cycle<br>Peak Current-Limit Threshold |                         | 0.6V < ILIM_ <2V                                                 | 30    |      | 100   | mV    |  |  |

| Peak Current-Limit Threshold<br>Programming Gain          |                         | 0.6V < ILIM_ <2V                                                 | 42.5  | 50   | 57.5  | mV/V  |  |  |

| ILIM_THRESHOLD                                            | LIM_ THRESHOLD          |                                                                  |       |      |       |       |  |  |

| Low-Voltage Threshold                                     |                         | Rising                                                           | 0.3   | 0.4  | 0.5   | V     |  |  |

| High-Voltage Threshold                                    |                         | Rising, with respect to V <sub>CCINT</sub>                       | -1.5  | -1   | -0.5  | V     |  |  |

| ILIMSEL THRESHOLD                                         |                         |                                                                  |       |      |       |       |  |  |

| Low-Voltage Threshold                                     |                         | Rising                                                           |       | 0.4  |       | V     |  |  |

| ERROR AMPLIFIER                                           |                         |                                                                  |       |      |       |       |  |  |

| Feedback Regulation Voltage                               | V <sub>FB</sub> _       |                                                                  | 786.5 | 800  | 813.5 | mV    |  |  |

| FB _ Input Leakage Current                                |                         | V <sub>FB</sub> _ = 0.8V, T <sub>A</sub> = T <sub>J</sub> = 25°C | -100  | 0    | +100  | nA    |  |  |

| Transconductance                                          | 9м_                     |                                                                  | 1.7   | 2    | 2.3   | mA/V  |  |  |

| POWER-GOOD OUTPUTS                                        |                         |                                                                  |       |      |       |       |  |  |

| PGOOD_ Threshold                                          | V <sub>FB</sub> rising  |                                                                  | 103   | 110  | 113   | % of  |  |  |

| PGOOD_THIESHOID                                           | V <sub>FB</sub> falling |                                                                  | 87    | 90   | 93    | FB_   |  |  |

| PGOOD_ Output Low Level                                   |                         | I <sub>PGOOD</sub> _ = 10mA                                      | 0.05  | 0.15 | 0.25  | V     |  |  |

| PGOOD_ Leakage Current                                    |                         | V <sub>PGOOD</sub> = 5V , T <sub>A</sub> = T <sub>J</sub> = 25°C | -100  |      | +100  | nA    |  |  |

| THERMAL SHUTDOWN                                          |                         |                                                                  |       |      |       |       |  |  |

| Thermal-Shutdown Threshold                                |                         |                                                                  |       | 160  |       | °C    |  |  |

| Thermal-Shutdown Hysteresis                               |                         |                                                                  |       | 20   |       | °C    |  |  |

Note 2: Limits are 100% tested at  $T_A = 25$ °C. Limits over the temperature range and relevant supply voltage range are guaranteed by design and characterization.

Note 3: This supply current excludes the switching current due to the external MOSFETs' gate charge.

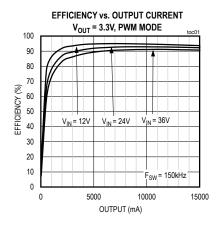

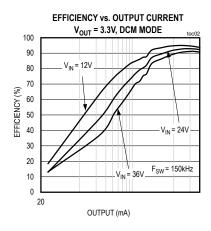

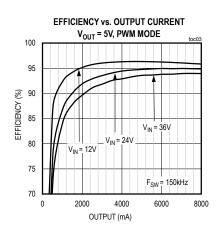

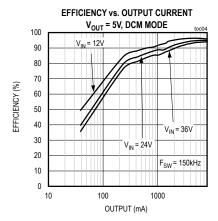

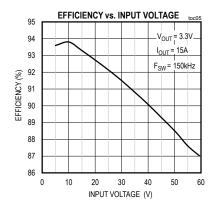

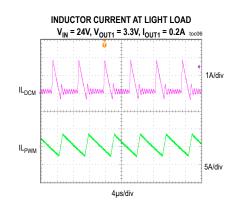

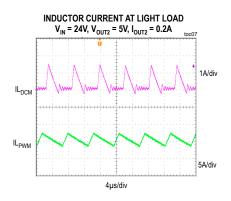

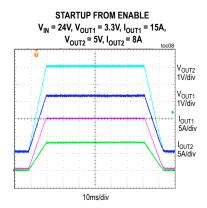

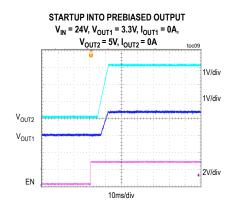

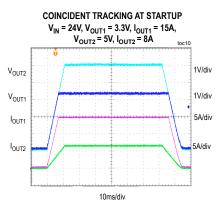

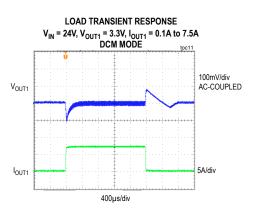

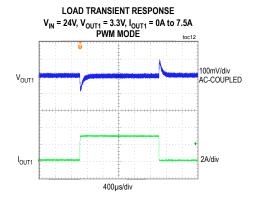

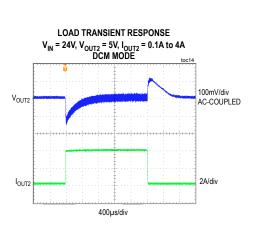

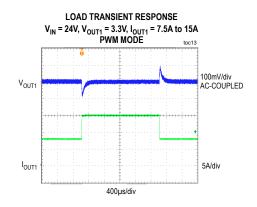

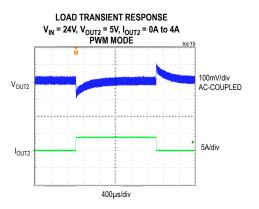

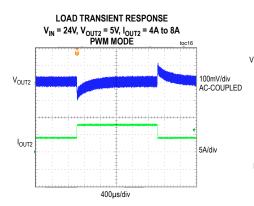

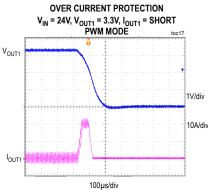

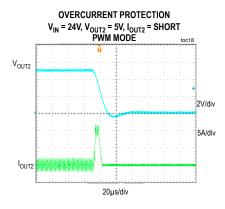

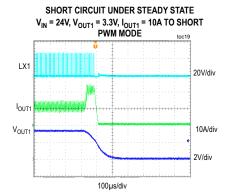

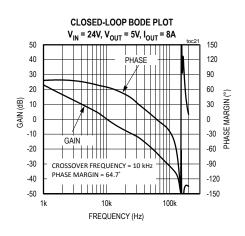

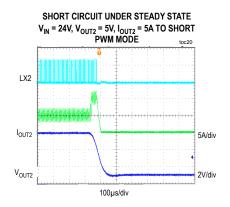

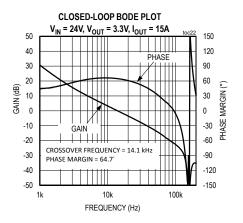

# **Typical Operating Characteristics**

(V<sub>IN</sub> = 24V, unless otherwise noted. See Figure 8.)

# **Typical Operating Characteristics (continued)**

(V<sub>IN</sub> = 24V, unless otherwise noted. See Figure 8.)

# **Typical Operating Characteristics (continued)**

(V<sub>IN</sub> = 24V, unless otherwise noted. See Figure 8.)

### **Typical Operating Characteristics (continued)**

$(V_{IN} = 24V, RT = unconnected, C_{VCCINT} = 4.7\mu F, EN1 = EN2 = unconnected, T_J = -40^{\circ}C to +125^{\circ}C, unless otherwise noted.)$

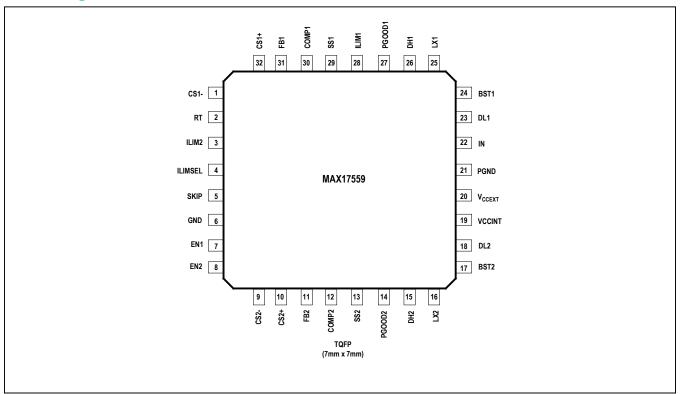

# **Pin Configuration**

# **Pin Description**

| PIN   | NAME         | FUNCTION                                                                                                                                                                                                                                                                  |

|-------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 9  | CS1-, CS2-   | Current-Sense Amplifier Negative Input of Controller 1 and Controller 2, Respectively. Connect to negative terminal of current-sense signal. See Figure 5 and Figure 6.                                                                                                   |

| 2     | RT           | Switching Frequency Programming Resistor Connection. Connect a resistor between RT and GND to set the switching frequency. See Figure 3. Connect to V <sub>CCINT</sub> to program switching frequency of 535kHz. Connect to GND to program switching frequency of 350kHz. |

| 3, 28 | ILIM2, ILIM1 | Current-limit Selection Inputs for Controller 2 and Controller 1. See the <i>Peak Current-Limit Programming (ILIM_)</i> section for a more detailed description.                                                                                                          |

| 4     | ILIMSEL      | Current-Limit Operating Mode Selection Input. Connect to GND or unconnected to select latchoff or foldback mode during overload/short circuit condition.                                                                                                                  |

| 5     | SKIP         | Connect SKIP to $V_{CCINT}$ to Select PWM Mode of Operation. Pull up SKIP with $100k\Omega$ to $V_{CCINT}$ or connect to a voltage between 1.25V and $V_{CCINT}$ - 1.5V to program DCM mode of operation. SKIP is internally pulled down to GND by $100k\Omega$ .         |

| 6     | GND          | Signal Ground Connection. GND should connect to the PGND plane at a single point. Refer to the MAX17559 evaluation kit data sheet PCB layout for an example grounding scheme.                                                                                             |

| 7, 8  | EN1, EN2     | Enable Input for Controller 1 and Controller 2. Either leave unconnected or connect to a voltage between 1.25V and 5.5V to enable corresponding controller. Connect to GND to disable corresponding controller.                                                           |

# **Pin Description (continued)**

| PIN    | NAME               | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                   |

|--------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10, 32 | CS2+, CS1+         | Current-Sense Amplifier Positive Input of Controller 2 and Controller 1. Connect to positive terminal of current-sense signal. See Figure 5 and Figure 6.                                                                                                                                                                                                                                  |

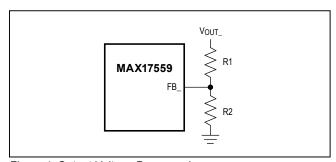

| 11, 31 | FB2, FB1           | Feedback Voltage Input of Controller 2 and Controller 1. Connect the FB_ pins to the midpoint of a resistor-divider from output to GND. See the circuit of Figure 4 for details.                                                                                                                                                                                                           |

| 12, 30 | COMP2,<br>COMP1    | Error Amplifier Output and Compensation Network-Connection Node for Controller 2 and Controller 1. Connect the COMP_ pins to the compensation network as shown in the circuit of Figure 7.                                                                                                                                                                                                 |

| 13, 29 | SS2, SS1           | Output Voltage Soft-Start/Stop Time Programming Pins. Connect a capacitor from SS_ to GND to program output-voltage soft-start/stop time. Alternatively, a resistor-divider on another voltage supply connected to this pin allows the device output to track the other supply during startup. See the Soft-Start/Soft Stop (SS_) and Soft-Start/Stop Capacitor sections for more details. |

| 14, 27 | PGOOD2,<br>PGOOD1  | Open-Drain Power-Good Pins of Controller 2 and Controller 1. Pull up with an external resistor to a maximum of 5.5V.                                                                                                                                                                                                                                                                       |

| 15, 26 | DH2, DH1           | High-Side MOSFET Driver Output of Controller 2 and Controller 1. Connect to gate of respective high-side MOSFET.                                                                                                                                                                                                                                                                           |

| 16, 25 | LX2, LX1           | Switching Node Connection Input of Controller 2 and Controller 1. Connect to respective output filter inductors.                                                                                                                                                                                                                                                                           |

| 17, 24 | BST2, BST1         | Bootstrap Capacitor Connection Input of Controller 2 and Controller 1. Connect a capacitor between BST_ and corresponding LX See the <i>Bootstrap Capacitor Selection</i> section for more details.                                                                                                                                                                                        |

| 18, 23 | DL2, DL1           | Low-Side MOSFET Driver Output of Controller 2 and Controller 1. Connect to gate of respective low-side MOSFET.                                                                                                                                                                                                                                                                             |

| 19     | V <sub>CCINT</sub> | Internal LDO Output. Connect a minimum 4.7µF low-ESR ceramic capacitor between V <sub>CCINT</sub> and PGND.                                                                                                                                                                                                                                                                                |

| 20     | V <sub>CCEXT</sub> | External Power Supply Input for Internal LDO. Apply a voltage between 4.85V and 24V to disconnect the LDO that operates from IN, and power internal circuitry with the LDO connected to $V_{CCEXT}$ . A minimum of $0.1\mu F$ local decoupling for the $V_{CCEXT}$ pin is recommended.                                                                                                     |

| 21     | PGND               | Power Ground. Connect to the source terminal of the external low-side MOSFETs and V <sub>CCINT</sub> bypass capacitor return terminal. Refer to the MAX17559 evaluation kit data sheet PCB layout for an example.                                                                                                                                                                          |

| 22     | IN                 | Supply Input. Bypass with minimum 1µF low-ESR ceramic capacitor to PGND.                                                                                                                                                                                                                                                                                                                   |

#### **Detailed Description**

The MAX17559 is a dual-output synchronous stepdown controller that operates from a 4.5V to 60V wide input supply range with programmable output voltage ranging from 0.8V to 24V. The IC uses constantfrequency, peak-current-mode control for the control loop. The frequency of the device can be adjusted from 100kHz to 2.2MHz using a resistor at the RT pin. Input capacitor size can be minimized by running the two outputs 180° out-of-phase.

The device provides independent adjustable soft-start/ stop and can start up monotonically with a prebiased output voltage. It also features selectable DCM/PWM mode of operation. Other features include independent open-drain PGOOD\_ outputs and independent enable (EN\_) inputs.

#### Internal LDO (VCCINT)

The IC has two internal 100mA low-dropout linear regulators that power  $V_{CCINT}.$  One regulator is powered from IN, while the other is powered from  $V_{CCEXT}.$  At any time, one of the two regulators is in operation depending on the voltage levels at  $V_{CCEXT}.$  If  $V_{CCEXT}$  voltage is greater than 4.7V (typ) then  $V_{CCINT}$  is powered from the  $V_{CCEXT}$  regulator. If  $V_{CCEXT}$  is lower than 4.55V (typ), then  $V_{CCINT}$  is powered from the IN regulator. Powering  $V_{CCINT}$  from  $V_{CCEXT}$  increases efficiency at higher input voltages.  $V_{CCEXT}$  can be connected to one of the switching regulator outputs if that output voltage is greater than 4.7V (typ). The maximum voltage limit on  $V_{CCEXT}$  is 24V.

$V_{CCINT}$  output voltage powers the gate drivers and internal control circuitry.  $V_{CCINT}$  should be decoupled to PGND with at least a 4.7µF low-ESR ceramic capacitor. The IC employs an undervoltage-lockout (UVLO) circuit that forces both the regulators off when  $V_{CCINT}$  falls below 3.8V (typ). The regulators are enabled again when  $V_{CCINT} > 4.2V$  (typ).

#### Low-Side Gate Driver (DL\_)

Low-side external MOSFET gate drivers are powered from  $V_{CCINT}$ . Under normal operating conditions, the low-side gate driver output (DL\_) is always the complement of the high-side gate driver output (DH\_). On each controller, dedicated circuitry monitors the DH\_ and DL\_ outputs and prevents either gate drive signal from turning on until the other gate drive signal is fully off. Thus, the circuit allows DH\_ to turn on only when DL\_ has been turned off. Similarly, it prevents DL\_ from turning on until DH\_ has been turned off.

There must be a low-impedance path from the DL\_ and DH\_ pins to the external MOSFET gates to ensure that the gate driver's circuitry works properly. To minimize impedance, very short, wide traces should be used in the PCB layout. The internal pulldown transistor that drives the DL\_ low is robust with a  $0.75\Omega$  (typ) on-resistance. This low on-resistance helps prevent DL\_ from being pulled up during the fast rising of the LX\_ node, due to capacitive coupling from the drain to the gate of the low-side synchronous rectifier MOSFET.

### High-Side Gate Driver (DH\_)

High-side gate drivers are powered from the bootstrap capacitors connected between BST\_ and LX\_. The bootstrap capacitor normally gets charged to  $V_{CCINT}$  during each switching cycle through an external schottky diode, when the low-side MOSFET turns on.

The high-side MOSFET is turned on by closing an internal switch between BST\_ and DH\_. This provides the necessary gate-to-source voltage to turn on the high-side MOSFET. See the <u>Bootstrap Capacitor Selection</u> section to choose the right size of the bootstrap capacitor.

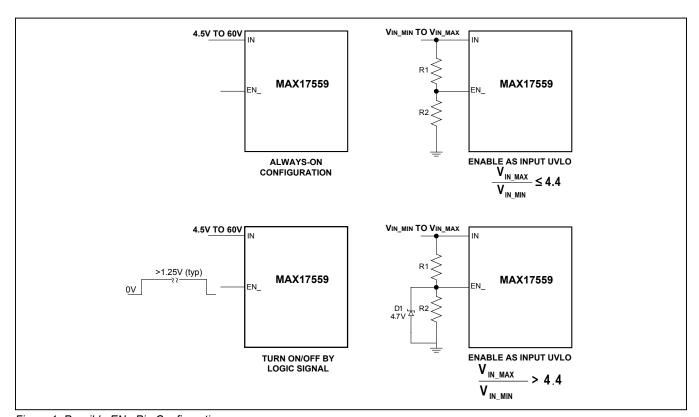

#### Shutdown and Enable (EN\_)

The two controllers of the IC can be independently shut down and enabled using the EN1 and EN2 pins. Pulling either of these pins below 1.25V (typ) shuts down the corresponding controller. Pulling both EN1 and EN2 below 0.7V disables both controllers and most internal circuits, including the  $V_{\mbox{\footnotesize{CCINT}}}$  LDOs. In this state, the device draws only  $10\mu\mbox{A}$  (typ) of quiescent current.

The EN\_ pin can be open or externally pulled up to a voltage between 1.25V (typ) and 5.5V to turn on the corresponding controller. Figure 1 shows the possible EN\_ pin configurations.

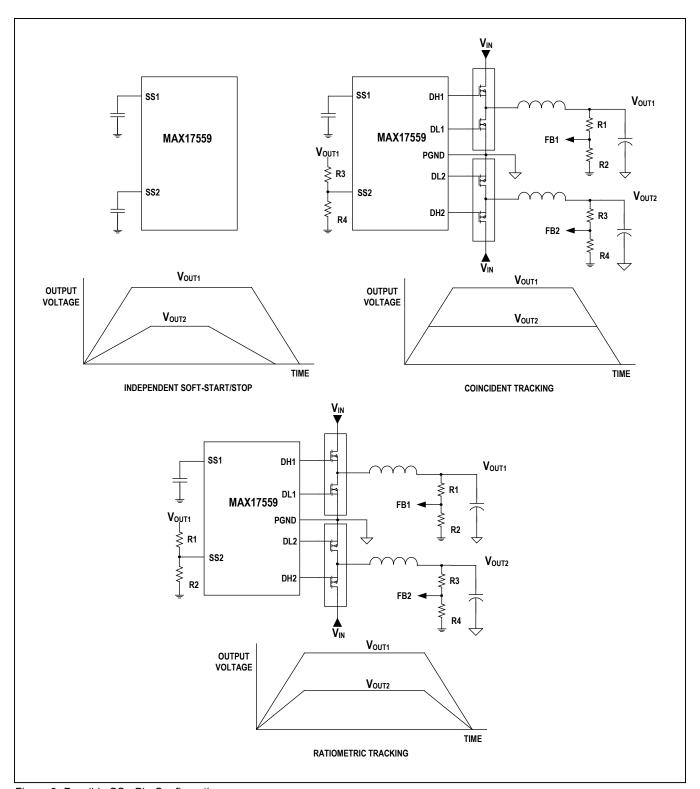

#### Soft Start/Stop (SS\_)

The soft-start/stop time of each controller's output voltage is controlled by the voltage on the relevant SS pin for that

controller. When the voltage on the SS\_ pin is less than the 0.8V internal reference, the device regulates the FB\_ voltage to the SS\_ pin voltage instead of the 0.8V internal fixed reference. This allows the SS\_ pin to be used to program the output voltage soft-start/stop time by connecting an external capacitor from the SS\_ pin to GND. An internal 5µA sourcing/sinking current charges/discharges this capacitor creating a voltage ramp on/off the SS\_ pin. As the SS\_ voltage rises linearly from 0 to 0.8V, the output voltage rises smoothly from zero to its final value and vice versa.

Alternatively, the SS\_ pin can be used to track the output to that of another supply at startup. This requires connecting the SS\_ pin to an external resistor-divider from the supply that needs to be tracked to GND. Figure 2 shows the possible ways of configuring the SS\_ pin.

Figure 1. Possible EN\_ Pin Configurations

Figure 2. Possible SS\_ Pin Configurations

#### **Light-Load Current Operation (SKIP)**

The MAX17559 can be configured to operate in either discontinuous-conduction mode (DCM) for high light-load efficiency or fixed-frequency pulse-width-modulation (PWM) mode. To select DCM, connect the SKIP pin to a DC voltage between 1.25V and  $V_{CCINT}-1.5V$ . To select the PWM mode of operation, connect SKIP to  $V_{CCINT}$ .

#### **DCM Mode**

In DCM, the device turns off the low-side MOSFET of the regulator close to the zero-crossing of the inductor current in each switching cycle. This operation minimizes negative current in the inductor, reducing loss due to current flowing from the output to the input. Therefore, the inductor current in each cycle is a triangular waveform whose peak is proportional to load current demand. The controller operates at a constant frequency while adjusting the peak current in the inductor for load and input voltage variations. However, under light-load and/or high input-voltage conditions, there exists a minimum on-time constraint for the controller. The minimum on-time is the smallest controllable pulse width that the controller can generate. This imposes a lower limit on the peak inductor current that can be programmed in the inductor and causes a fixed amount of energy to be delivered to the output, regardless of the energy requirement of the load. If the load is such that the amount of energy delivered during minimum on-time is more than the load energy, the output voltage rises above its nominal set value. This results in skipping of switching cycles to regulate the average output voltage to the set point. This operation results in an effective switching frequency that is lower than the programmed switching frequency, which improves the regulator efficiency. As the load

current increases to a point where the valley of the inductor current rises above zero, the regulator operation moves into PWM mode.

#### **PWM Mode**

Each controller of the device operates in PWM mode whenever SKIP is connected to V<sub>CCINT</sub>. The inductor current is allowed to go negative in this mode. In PWM mode, under normal operating conditions, the high-side MOSFET turns on at an edge of the internal clock. An internal error amplifier compares the feedback voltage at the FB pin to a fixed internal reference voltage and generates an error current. This error current flows through the compensation network at the COMP pin and generates control voltage for the inner current loop. The on-time of the high-side MOSFET in a switching cycle is determined by comparing the control voltage at the COMP pin with the sum of the current-sense voltage at CS\_+, CS\_-, and the internal slope-compensation voltage. The inductor current ramps up during the highside MOSFET turn-on time. Once the high-side MOSFET is turned off, the low-side MOSFET is turned on. During low-side MOSFET turn-on time, the inductor current ramps down. The low-side MOSFET remains on until the next clock edge. The PWM mode of operation has the advantages of low output-voltage ripple and constant frequency operation, which is beneficial in applications that are sensitive to operating frequency. Under minimum on-time conditions described in the DCM Mode section, the device skips high-side turn-on events in PWM mode also, to regulate the output voltage. This results in lowfrequency operation with regard to inductor current and output-voltage-ripple waveforms.

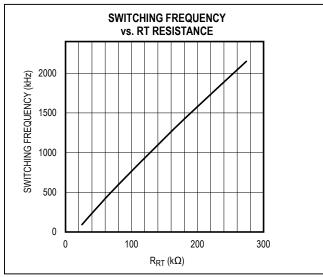

#### Frequency Selection (RT)

The selection of switching frequency is a tradeoff between efficiency and components size. Low-frequency operation increases efficiency by reducing MOSFET switching losses and gate-drive losses, but requires a larger inductor and/or capacitor to maintain low output ripple voltage. The switching frequency of the device can be programmed between 100kHz to 2.2MHz using the RT pin. Connect RT to  $V_{\rm CCINT}$  to program a default frequency of 535kHz switching frequency and to GND to program 350kHz switching frequency. Figure 3 shows the switching frequency for different RT values.

The following formula can be used to find the required resistor for a give switching frequency.

$$R_{RT} = \frac{f_{SW} + 133}{8.8}$$

#### 180° Phase Operation

The IC provides a fixed 180° phase-shift operation between two output channels to have advantages of:

- Reduction of input and output capacitor RMS current.

- Lower input-voltage ripple.

#### **Output Overvoltage Protection**

The output overvoltage-protection circuit protects the load under output overvoltage conditions. If the output voltage rises by more than 10% of its nominal value, the high-side MOSFET is turned off until the overvoltage condition clears.

The state of the low-side MOSFET during output overvoltage conditions depends on the selected operating

Figure 3. RT vs. Switching Frequency

mode. If PWM mode is selected, the low-side MOSFET remains on until the output overvoltage condition clears. In this case, the current through the low-side MOSFET can reach a large value depending on the amount of overvoltage and output capacitance. If DCM is selected, the low-side MOSFET is turned off whenever the inductor current reaches zero. In this mode, the low-side MOSFET is turned on every 10 clock cycles to refresh the BST\_capacitor. This causes a slightly negative average inductor current which, in addition to the load current present, can slowly discharge the output.

#### Power-Good (PGOOD1 and PGOOD2) Pins

The IC features independent open-drain power-good (PGOOD1, PGOOD2) pins. The PGOOD\_ pins pull low when the corresponding FB\_ pin voltage is outside ±10% of the 0.8V reference voltage. During soft-start, PGOOD\_ is low. When the FB\_ pin voltage is within the -10% of the reference voltage, PGOOD\_ is allowed to be pulled up by an external resistor to a source voltage no greater than 6V.

#### **Operation under Current Limit (ILIMSEL)**

The device features the following selectable operating modes ( $\underline{\text{Table 1}}$ ) under current-limit conditions based on ILIMSEL configuration.

Independent of current-limit mode being selected, whenever the inductor peak current reaches the current limit threshold, the high-side MOSFET is turned off immediately and the the low-side MOSFET is turned on. The MAX17559 forces the low-side MOSFET on until the current-limit condition is cleared. Under current-limit conditions, the output voltage starts to drop from its steady-state value. Depending on the current-limit mode selected, once the output voltage drops below 70% of its set value, the device enters either foldback or latchoff mode.

#### Foldback Current Limit (ILIMSEL = Unconnected)

Under overload conditions, when the output voltage falls to less than 70% of its nominal level, foldback current limiting is activated. In this mode, the peak inductor current is progressively lowered from 100% to 50% of the programmed value, in proportion to the FB\_ voltage. Foldback current-limit mode is disabled during the soft-start/stop duration.

**Table 1. Selection Mode of Current Limit**

| ILIMSEL PIN CONFIG- | MODE OF OPERATION UNDER |

|---------------------|-------------------------|

| URATION             | CURRENT LIMIT CONDITION |

| Float               | Foldback                |

| GND                 | Latchoff                |

#### **Latchoff Mode Operation (ILIMSEL = GND)**

Under an overcurrent limit condition, whenever the output voltage drops below 70% of its set value, the controller enters latchoff mode and both the high and low-side MOSFETs are kept off. The latchoff is not active during soft-start. The controller will remain idle until the corresponding EN\_ pin or the IC supply is cycled to GND and activated again.

#### Peak Current Limit Programming (ILIM\_)

The device features an adjustable peak-current-limit threshold independently for each controller. Connect a resistor from ILIM to GND to program current limit.

The resistor value can be calculated using the following formula:

$$R_{ILIM\_(k\Omega)} = \frac{ILIM\_THRESHOLD}{(I_{ILIM} \times 50)}$$

where  $I_{\text{ILIM}\_}$  is the internal current source at the ILIM\_ pin (5µA).

ILIM\_Threshold can be calculated using the following formula:

$$ILIM\_THRESHOLD = \left[ILOAD_{MAX} + \frac{\Delta I_{LPK-PK(MAX)}}{2}\right] \times R_{SENSE}$$

where  $ILOAD_{MAX}$  is the maximum load current.

Where  $I_{LPK-PK(MAX)}$  is the maximum inductor ripple current and can be calculated as follows:

$$\Delta I_{LPK-PK}(max) = \frac{V_{OUT} * \left[1 - \frac{V_{OUT}}{V_{INMAX}}\right]}{L * F_{SW}}$$

R<sub>SENSE</sub> is the current sense resistor.

The maximum programmable value of the  $I_{LIM\_Threshold}$  is 100mV.

The device also has two selectable, cycle-by-cycle positive current limit thresholds based on ILIM\_ configuration. Table 2 gives cycle-by-cycle positive current limit thresholds based on the ILIM\_ pin configuration.

Table 2. Peak Current-Limit Thresholds for Different ILIM Settings

| ILIM PIN<br>CONFIGURATION | POSITIVE CURRENT-LIMIT<br>THRESHOLD (TYP) |

|---------------------------|-------------------------------------------|

| V <sub>CCINT</sub>        | 75mV                                      |

| GND                       | 30mV                                      |

#### **Startup Into Prebiased Output**

The IC supports monotonic startup into a prebiased output voltage. During startup, if the FB\_ pin voltage is higher than the SS\_ pin voltage, the high-side MOSFET is held off and the low-side MOSFET is turned on for a duration of 150ns for every 10 clock cycles to refresh the BST\_ capacitor. This causes a slightly negative average inductor current, which can slowly discharge the output. Once the SS\_ pin voltage reaches the FB\_ voltage, normal soft-start operation occurs, and the output voltage smoothly ramps up from the prebiased value.

#### **Operating Input Voltage Range**

For a step-down converter, the minimum and maximum operating input voltages for a given output voltage should be calculated as follows:

$$V_{IN\_MIN} = \frac{V_{OUT} + I_{LOAD(MAX)} \times (R_{DS(ON)\_LOW} + DCR)}{1 - f_{SW\_MAX} \times t_{OFF\_MIN}} + L_{OAD(MAX)} \times (R_{DS(ON)} + H - R_{DS(ON)} + L_{OAD(MAX)} \times (R_{DS(ON)} + H - R_{DS(ON)} + R_{DS(ON)$$

$$V_{IN\_MAX} = \frac{V_{OUT}}{(f_{SW MAX} \times t_{ON MIN})}$$

where  $V_{OUT}$  is the steady-state output voltage,  $I_{LOAD(MAX)}$  is the maximum load current, DCR is the DC resistance of the inductor,  $f_{SW\_MAX}$  is the maximum switching frequency,  $R_{DS(ON)\_HI}$  and  $R_{DS(ON)\_LOW}$  are the on-state resistances of the high-side and low-side MOSFETs,  $t_{OFF\_MIN}$  is the worst-case minimum off-time (160ns), and  $t_{ON\_MIN}$  is the worst-case minimum on-time (155ns) from the *Electrical Characteristics* table.

#### **Thermal-Overload Protection**

Thermal-overload protection limits total power dissipation in the IC. When the junction temperature of the device exceeds +160°C, an on-chip thermal sensor shuts down the device, allowing the device to cool. The thermal sensor turns the device on again once the junction temperature cools by 20°C. The device restarts with soft-start when recovering from thermal shutdown.

#### **Applications Information**

#### Setting the Input Undervoltage-Lockout Level

The EN pins can be used as input undervoltage-lockout detectors with a typical hysteresis of 100mV. As shown in Figure 1, the input voltage at which each controller of the IC turns on can be set with a resistor-divider connected to the corresponding EN from IN to GND.

Select R2 =  $10k\Omega$  and calculate the R1 based on the following equation:

R1 = R2

$$\times \frac{(VIN_{UVLO} - 1.25)}{1.25}$$

where VIN<sub>UVI O</sub> is the input voltage at which the controller should be enabled.

#### Setting the Output Voltage

The output voltage of each controller is set by connecting a resistor-divider to FB from the corresponding output to GND (Figure 4). Using the following equation, select R1 based on the offset introduced on the output voltage by the FB leakage. Let  $\alpha$  be the offset introduced on the output voltage:

$$R1 \le \frac{\alpha}{I_{FB}}$$

where IFB is the FB\_leakage current (±100nA max). For example, for  $V_{OUT}$  = 5V,  $\alpha$  = 0.1% of  $V_{OUT}$  (= 5mV):

$$R1 \le \frac{5mV}{0.1\mu A}$$

$R1 \leq 50k\Omega$

Calculate R2 with the following equation:

$$R2 = \frac{R1}{\left(\frac{V_{OUT}}{0.8} - 1\right)}$$

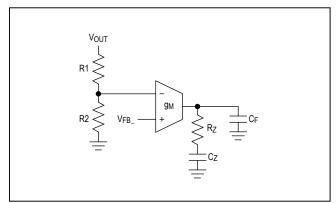

Figure 4. Output-Voltage Programming

#### **Soft-Start/Stop Capacitor**

Soft-start/stop time is programmed by connecting a capacitor from the SS\_ pin to GND. An internal 5µA current source charges/discharges the capacitor at the SS pins providing a linear ramping voltage for output-voltage reference. The soft-start time is calculated based on the following equation:

$$t_{SS} = C_{SS} \times \frac{0.8 \, \text{V}}{5 \mu \text{A}}$$

#### Inductor Selection

Three key inductor parameters must be specified to select the output inductor.

- 1) Inductance (L).

- 2) Inductor saturation current (I<sub>SAT</sub>).

- DC resistance of inductor (DCR).

The required inductance (L) is calculated based on the ratio of inductor peak-to-peak ripple AC current to its DC average current (LIR). A good compromise between size and loss is a 30% peak-to-peak ripple current to average-current ratio (LIR = 0.3). The switching frequency, input voltage, output voltage, and selected LIR then determine the inductor value as follows:

$$L = \frac{V_{OUT} \times (1-D)}{LIR \times I_{LOAD} \times f_{SW}}$$

where V<sub>OUT</sub> is the output voltage, D is the operating duty cycle (= V<sub>OUT</sub>/V<sub>IN</sub>), I<sub>LOAD</sub> is the full-load current, and f<sub>SW</sub> is the operating switching frequency.

The minimum inductor saturation current should be equal to or greater than maximum inductor peak current that is given by the following equation:

$\begin{array}{l} \text{Maximum Inductor} \\ \text{Peak Current} \end{array} = \\ \text{Maximum Load Current} + \Delta I_{LPK} \left( \text{max} \right) \end{array}$

where  $\Delta I_{IPK-PK}$  (max) is the maximum inductor ripple current and can be calculated as follows:

$$\Delta I_{LPK-PK} (max) = \frac{V_{OUT} \times \left[1 - \frac{V_{OUT}}{V_{INMAX}}\right]}{L \times f_{SW}}$$

Selecting an inductor with lower DCR improves efficiency, but there is a lower limit for DCR based on the minimum peak-to-peak current-sense signal required at the currentsense pins, as described in the Current Sensing (CS\_+ and CS -) section.

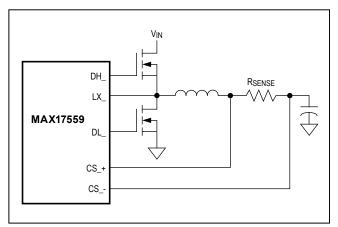

#### Current Sensing (CS\_+ and CS\_-)

The CS\_+ and CS\_- pins are the inputs to the internal current-sense amplifiers. The common-mode operating voltage range on these pins is 0 to 24V, enabling the IC to regulate output voltages up to a nominal 24V.

Whether the current-sensing is performed by an external current-sense resistor or inductor DCR, the desired current-sense resistance is calculated using the following equation:

$$R_{SENSE} = \frac{V_{CS}}{I_{LOAD(MAX)} + \frac{\Delta I_{LPK-PK} (max)}{2}}$$

where R<sub>SENSE</sub> is the desired current-sense resistor,  $V_{CS}$  is the selected current-limit threshold based on ILIM pin setting, and  $I_{LOAD(MAX)}$  is the maximum load current.

To ensure that the application delivers a full-load current over the full operating temperature range, select the minimum value for the  $V_{CS}$  parameter from the <u>Electrical</u> Characteristics table.

It should be noted that the magnitude of current-sense ripple voltage is critical for a good signal-to-noise ratio to ensure minimum duty-cycle jitter. The worst-case current-sense ripple voltage occurs at the minimum operating input voltage and should be set in the 7mV to 12mV range. The following equation can be used to calculate the worst-case current-sense ripple voltage at the CS\_+, CS\_- pins:

$$\Delta V_{CSMIN} = \Delta I_{LPK-PK(MIN)} \times R_{SENSE}$$

where  $\Delta I_{LPK-PK(MIN)}$  is the minimum inductor current ripple that occurs at the minimum operating input voltage.  $\Delta I_{LPK-PK(MIN)}$  can be calculated using the following equation:

$$\Delta I_{LPK-PK(MIN)} = \frac{V_{OUT} \times \left[1 - \frac{V_{OUT}}{V_{INMIN}}\right]}{L \times f_{SW}}$$

If  $\Delta V_{CSMIN}$  is less than the target value, the selected output inductance should be lowered and R<sub>SENSE</sub> should be iteratively re-calculated until  $\Delta V_{CSMIN}$  is greater than or equal to the target value (7mV to 10mV, depending on PCB layout).  $V_{CS(MAX)}$ , as calculated by the following equation, is less than the selected  $V_{CS}$  from the Electrical Characteristics table.

$$V_{CS(MAX)} = R_{SENSE} \times \left[ I_{LOADMAX} + \frac{\Delta I_{LPK-PK}(max)}{2} \right]$$

Because of PCB layout-related noise, operation at the minimum operating voltage should be checked for jitter before finalizing the worst-case current-sense voltage. Care should be taken to ensure that current-sense filter components be placed close to the IC's current-sense pins. The current-sense traces should be short and differentially routed.

#### **Current Sensing Using an External Sense Resistor**

A typical current-sensing circuit using a discrete resistor is shown in <u>Figure 5</u>. The power rating of R<sub>SENSE</sub> should be selected using the following equation for dissipation in R<sub>SENSE</sub>:

Power losses in

$$R_{SENSE} = \left[I_{LOAD}^2 + \left(\frac{\Delta IL^2}{12}\right)\right] \times R_{SENSE}$$

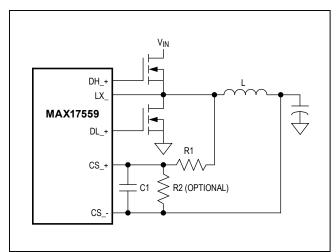

Figure 5. Current Sensing Using an External Sense Resistor

#### **Current Sensing Using Inductor DCR**

Current sensing using inductor DCR current improves the system efficiency compared to current sensing using an external sense resistor. The disadvantage of DCR current-sensing is that the current limit is not as accurate when compared to the sense resistor because of wider variation of the inductor DCR over temperature and initial tolerance specified by manufacturers. A typical DCR current-sensing circuit is shown in Figure 6. Place C1 across the CS\_ pins. Usually, C1 is selected in the  $0.1\mu F$  to  $0.47\mu F$  range. Calculate R1 (if R2 is not used) based on following equation:

$$R1 = \frac{L}{DCR \times C1}$$

R2 is used in applications where the DCR of inductor is greater than the desired current-sense resistance. In this case, calculate R1 and R2 using the following equation:

$$RP = \frac{L}{DCR \times C1}$$

where RP is the parallel combination of R1 and R2 (=  $[R1 \times R2]/[R1 + R2]$ ).

$$R1 = \frac{DCR \times RP}{R_{SENSE}}$$

$$R2 = \frac{R1 \times RP}{R1 - RP}$$

Figure 6. Typical Current Sensing Using Inductor DCR

#### **Input Capacitor Selection**

The input filter capacitor reduces peak currents drawn from the power source and reduces noise and voltage ripple on the input caused by the circuit's switching. Use low-ESR ceramic capacitors at the input. For each output channel, calculate the input capacitance required for a specified input-ripple  $\Delta$ VIN using the following equations by neglecting the ripple component due to ESR of input capacitor:

$$C_{IN} = \frac{I_{LOAD} \times D \times (1-D)}{\eta \times \Delta VIN \times f_{SW}}$$

where D =  $(V_{OUT}/V_{IN})$ ,  $\eta$  is efficiency of power conversion.

The input capacitor RMS current requirement (CIN<sub>RMS</sub>) can be calculated by the following equation:

$$CIN_{RMS} = I_{LOAD(MAX)} \times \sqrt{D \times (1-D)}$$

where,  $I_{LOAD(MAX)}$  is the maximum value of load current, D =  $V_{OLIT}/V_{IN}$ .

#### **Output Capacitor Selection**

The key selection parameters for the output capacitor are capacitance value, ESR, and voltage rating. These parameters affect the overall stability, output ripple voltage, and transient response. The steady-state output ripple  $(\Delta V_{OUTSS})$  has two components (by neglecting the ESL of the output capacitors): one component is due to the voltage drop across the ESR  $(\Delta V_{OUTESR\_SS})$ , while the other component is due to the variation in charge stored in the output capacitor  $(\Delta V_{OUTQ\_SS})$ . By neglecting the output voltage drop due to the ESL of output capacitor, approximate output voltage ripple under steady-state is given by:

$$\Delta V_{OUTSS} \approx \Delta V_{OUTESR\_SS} + \Delta V_{OUTQ\_SS}$$

where  $\Delta V_{\mbox{OUTSS}}$  is the output-voltage ripple under steady state:

$$\Delta V_{OUTESR\_SS} = \Delta IL_{PK-PK} \times ESR$$

$$\Delta V_{OUTQ\_SS} = \frac{\Delta IL_{PK-PK}}{8 \times f_{SW} \times C_{OUT}}$$

Calculate the required C<sub>OUT</sub> and ESR based on the above equations. For ceramic output capacitors,  $\Delta V_{OUTQ\_SS}$  contributes to approximately 80% of the total output ripple voltage ( $\Delta V_{OUTSS}$ ). For electrolytic output capacitor,  $\Delta V_{OUTQ\_SS}$  contributes approximately 50% of the total output-voltage ripple. Low ESR capacitors should be used.

#### **Loop Compensation**

The IC uses an internal transconductance error amplifier with its inverting input and its output available to the user for external frequency compensation. The output capacitor and compensation network determine the loop stability for a given output inductor and output capacitor.

The controller uses a peak-current-mode-control scheme that regulates the output voltage by forcing the required current through the external inductor. Current-mode control eliminates the double pole in the feedback loop caused by the inductor and output capacitor, in the case of voltage mode control, resulting in a smaller phase-shift and requiring less elaborate error-amplifier compensation. Typical type-2 compensation used with peak current-mode control is shown in  $\underline{\text{Figure 7}}$ . Calculate the compensation resistor (Rz) using the following equation:

$$R_Z = \frac{2 \times \pi \times f_{CO} \times C_{OUT} \times G_{CS} \times R_{SENSE}}{g_M \times G_{FB}}$$

where  $f_{CO}$  is the desired crossover frequency that should be chosen between  $f_{SW}/10$  and  $f_{SW}/20$ ,  $C_{OUT}$  is the output capacitance,  $G_{CS}$  is the current-sense amplifier gain, which depends on the ILIM setting,  $R_{SENSE}$  is the effective current-sense resistor across the  $CS_+$  and  $CS_-$  pins,  $g_M$  is the internal transconductance amplifier gain,  $G_{FB}$  is the output-voltage feedback divider gain, which is equal to  $(0.8V/output\ voltage)$ .

Figure 7. Typical Type-2 Compensation Network

C<sub>7</sub> is calculated using the following equation:

$$C_Z = \frac{1}{2 \times \pi \times f_{P\_Load} \times R_Z}$$

where  $f_{P\_Load}$  is the load-pole frequency approximated by the following equation:

$$f_{P\_Load} = \frac{1}{2 \times \pi \times C_{OUT} \times \left(\frac{V_{OUT}}{I_{LOAD}}\right)}$$

Calculate C<sub>F</sub> using the following equation:

$$C_{F} = \frac{1}{2 \times \pi \times R_{Z} \times f_{P\_EA}}$$

where  $f_{P\_EA}$  is the pole frequency created by  $R_Z$  and  $C_F$  given by the minimum of ESR zero frequency given by the following equation or  $f_{SW}/2$ :

$$f_{Z\_ESR} = \frac{1}{2 \times \pi \times C_{OUT} \times ESR}$$

When the output capacitor is composed of n identical capacitors in parallel, the resulting  $C_{OUT}$  = n ×  $C_{OUT}$  (each), and ESR = ESR (each)/n. Note that the location of  $f_{Z\_ESR}$  for a parallel combination of same capacitors is the same as for an individual capacitor.

#### **Bootstrap Capacitor Selection**

The selected high-side nMOSFET determines the appropriate bootstrap capacitance values according to the following equation:

$$C_{BST} = \frac{\Delta Q_{Gate}}{\Delta V_{BST}}$$

where  $\Delta Q_{Gate}$  is the total gate charge of the high-side MOSFET and  $\Delta V_{BST}$  is the voltage variation allowed on the high-side MOSFET driver after turn-on. Choose  $\Delta V_{BST}$  so the available gate-drive voltage is not significantly degraded (e.g.,  $\Delta V_{BST}$  = 100mV) when determining  $C_{BST}$ . The bootstrap capacitor should be a low-ESR ceramic capacitor. A minimum value of 100nF is recommended.

# 60V, Dual-Output, Synchronous Step-Down Controller

#### **MOSFET Selection**

Each controller drives two external, logic-level nMOSFETs as the circuit switch elements. The key selection parameters to choose these MOSFETs include:

- On-resistance (R<sub>DS(ON)</sub>).

- Maximum drain-to-source voltage (V<sub>DS</sub>(MAX)).

- Miller Plateau voltage on HSMOSFET Gate (V<sub>MII</sub>).

- Total gate charge (Q<sub>Gate</sub>).

- Output capacitance (C<sub>OSS</sub>).

- Power dissipation rating and package thermal resistance

Both nMOSFETs must be logic-level types with guaranteed on-resistance specifications at  $V_{GS}$  = 4.5V. The duty cycles for the high and low-side external MOSFETs can be calculated as follows:

High-side MOSFET duty cycle:

$$D = \frac{V_{OUT}}{V_{INI}}$$

Low-side MOSFET duty cycle = 1 - D

High-side MOSFET losses can be approximated using the following formula:

$$P_{HSMOSFET} = P_{HSMOSFET\_Conduction} \\ + P_{HSMOSFET\_Switching} \\ P_{HSMOSFET\_Conduction} = I_{LOAD(MAX)}^2 \\ \times R_{DS(ON)} * D \\ \\ \begin{bmatrix} V_{IN} \times I_{LOAD(MAX)} \\ 2 \\ \times \hline V_{CCINT} - V_{MIL} \end{bmatrix} \\ + [V_{IN} \times Q_{rr}] + \\ \begin{bmatrix} (1/2) \times C_{OSSHS} \times V_{IN}^2 \\ + [(1/2) \times C_{OSSLS} \times V_{IN}^2] \end{bmatrix} \\ \end{bmatrix}$$

where:

f<sub>SW</sub> is the operating switching frequency,

$I_{LOAD(MAX)}$  is the maximum load current in the application,  $Q_{SW}$  is the switching charge of the high-side MOSFET, which can be obtained from the MOSFET data sheet,

R<sub>DR</sub> is the sum of the DH pin driver resistance and the HSMOSFET internal gate resistance,

$V_{MIL}$  -  $V_{GS}$  on HSMOSFET gate that produces  $I_{DS}$  =  $I_{LOAD(MAX)}$

$Q_{rr}$  is the reverse-recovery charge of the low-side MOSFET body diode (if external Schottky is not placed across low-side MOSFET),

$\mathsf{C}_{\mbox{\scriptsize OSSHS}}$  is the effective output capacitance of the high-side MOSFET,

$\mathsf{C}_{\mbox{OSSLS}}$  is the effective output capacitance of the low-side MOSFET.

Low-side MOSFET losses can be approximated using the following formula:

$$\begin{aligned} P_{HSMOSFET} = & I_{LOAD(MAX)}^{2} \times R_{DS(ON)} \times (1-D) \\ &+ V_{D} \times I_{LOAD(MAX)} \times t_{DT} \times f_{SW} \end{aligned}$$

where,  $V_D$  is the forward-drop of the LSMOSFET body diode and  $t_{DT}$  is the dead time from the <u>Electrical</u> Characteristics table.

Take the  $R_{DS(ON)}$  variation with temperature into account while calculating the above losses and ensure that the losses of each MOSFET do not exceed their power rating. Using a low  $Q_{rr}$  Schottky diode across the low-side MOSFET reduces the high-side MOSFET losses.

#### **Power Dissipation Within the MAX17559**

Gate-charge losses are dissipated by the drivers. Therefore, the gate-driver current taken from the internal LDO regulator and resulting power dissipation must be checked. If  $V_{CCEXT}$  is not used to power  $V_{CCINT}$ , calculate the approximate IC losses as follows:

$$P_{MAX17559} = V_{IN} \times \lceil (Q_{Gate} \times f_{SW}) + I_{IN} \rceil$$

If  $V_{CCEXT}$  is used to power the  $V_{CCINT}$ , use the following equation to calculate the approximate IC losses:

$$P_{MAX17559} = V_{CCEXT} \times \left[ (Q_{Gate} \times f_{SW}) + I_{IN} \right]$$

where.

$Q_{Gate}$  = Total gate charge of high-side and low-side MOSFETs of controller1 + total gate charge of high-side and low-side MOSFETs of controller 2,

$I_{\mbox{\scriptsize IN}}$  is the supply current given in the <u>Electrical</u> Characteristics table.

#### MAX17559

# 60V, Dual-Output, Synchronous Step-Down Controller

Calculate the IC junction temperature using the following equation and ensure that this value does not exceed +125°C:

$$T_J = [P_{MAX17559} \times Rth_{JA}] + T_A$$

where:

T<sub>J</sub> is the IC junction temperature,

P<sub>MAX17559</sub> is the power losses in the IC,

Rth<sub>JA</sub> is the IC junction-to-ambient thermal resistance, which is typically 29°C/W for a multilayer board.

T<sub>A</sub> is the maximum ambient temperature.

#### **PCB Layout Guidelines**

Careful PCB layout is critical to achieve low losses, low output noise, and clean and stable operation. Use the following guidelines for PCB layout:

- Keep input bypass capacitors as close as possible across the drain of the high-side MOSFET and source of the low-side MOSFET.

- If external Schottky diodes are used across the lowside MOSFET, keep the Schottky very close and right across the low-side MOSFET.

- Keep IN, V<sub>CCINT</sub>, V<sub>CCEXT</sub> bypass capacitors and BST capacitors nearer to IC pins.

- Route high-speed switching nodes (BST\_, LX\_, DH\_, and DL\_) away from the sensitive analog areas (RT, COMP\_, CS\_, and FB\_).

- The gate current traces must be short and wide. Use multiple small vias to route these signals if routed from one layer of the PCB to another layer.

- Route current-sense lines parallel, short, and next to each other to minimize the loop formed by these lines.

- Keep current-sense filter capacitors nearer to IC current-sense pins and on the same side of the IC.

- Group all GND-referred and feedback components close to the IC.

- Keep the FB\_ and compensation network nets as small as possible to prevent noise pickup.

- If possible, place all power components on the top side of the board and run the power-stage currents using traces or copper fills on the top side only, without adding vias.

- Keep the power traces and load connections short.

This practice is essential for high efficiency. Use thick copper PCBs (2oz or higher) to enhance efficiency and minimize trace inductance and resistance.

- On the top side, lay out a large PGND copper area for the output and connect the bottom terminals of the input bypass capacitors, output capacitors, and the source terminals of the low-side MOSFET to that area.

- Refer to the MAX17559 evaluation kit data sheet PCB layout for an example.

# **Typical Application Circuits**

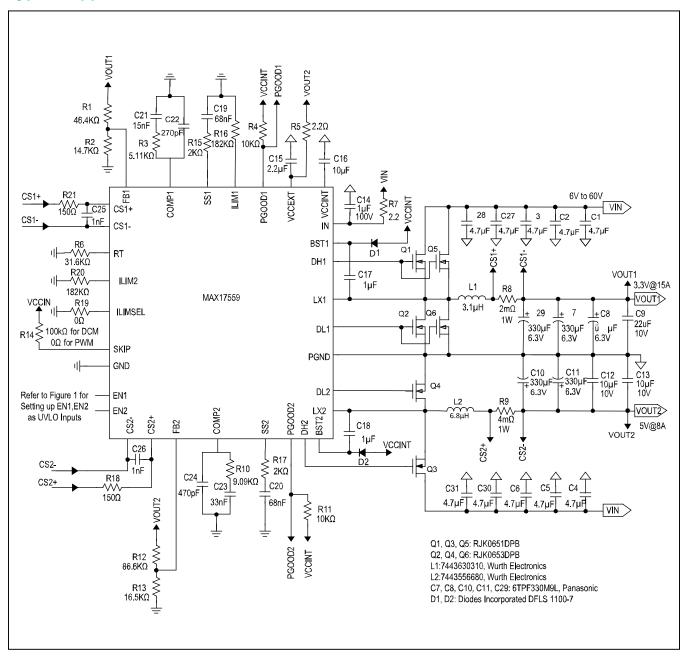

Figure 8. Wide-Input Voltage, High-Efficiency 5V and 3.3V Output Buck Converter with Resistor-Based Current Sensing (R8, R9).

# **Typical Application Circuits (continued)**

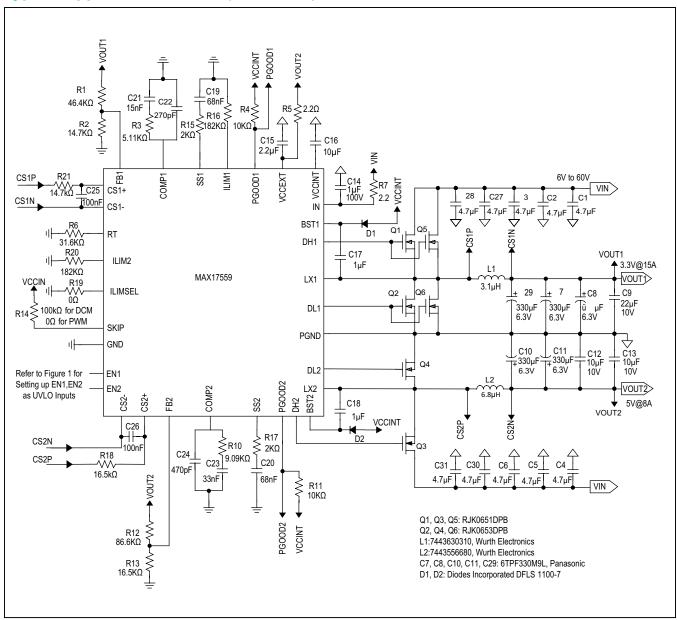

Figure 9. Wide Input Voltage, High-Efficiency 5V and 3.3V Output Buck Converter with Inductor DCR Current Sensing (L1, L2).

# **Ordering Information**

| PART         | TEMP RANGE      | PIN-PACKAGE            |

|--------------|-----------------|------------------------|

| MAX17559ACJ+ | -40°C to +125°C | 32 TQFP<br>(7mm x 7mm) |

## **Chip Information**

PROCESS: BICMOS

# **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE | OUTLINE | LAND        |

|---------|---------|---------|-------------|

| TYPE    | CODE    | NO.     | PATTERN NO. |

| 32 TQFP | C32+3   | 21-0292 | 90-0297     |

### MAX17559

# 60V, Dual-Output, Synchronous Step-Down Controller

# **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 6/15          | Initial release | _                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.