Wired Communications

Edition 2001-11-20

Published by Infineon Technologies AG, St.-Martin-Strasse 53, D-81541 München, Germany

© Infineon Technologies AG 2001.

All Rights Reserved.

# Attention please!

The information herein is given to describe certain components and shall not be considered as warranted characteristics.

Terms of delivery and rights to technical change reserved.

We hereby disclaim any and all warranties, including but not limited to warranties of non-infringement, regarding circuits, descriptions and charts stated herein.

Infineon Technologies is an approved CECC manufacturer.

### Information

For further information on technology, delivery terms and conditions and prices please contact your nearest Infineon Technologies Office in Germany or our Infineon Technologies Representatives worldwide (see address list).

### Warnings

Due to technical requirements components may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies Office.

Infineon Technologies Components may only be used in life-support devices or systems with the express written approval of Infineon Technologies, if a failure of such components can reasonably be expected to cause the failure of that life-support device or system, or to affect the safety or effectiveness of that device or system. Life support devices or systems are intended to be implanted in the human body, or to support and/or maintain and sustain and/or protect human life. If they fail, it is reasonable to assume that the health of the user or other persons may be endangered.

# SWITI Switching IC

PEF 20450 MTSI

PEF 20470 MTSI-L

PEF 24470 MTSI-XL

Version 1.3

Wired Communications

PEF 20450 / 20470 / 24470

**PRELIMINARY**

Revision History: 2001-11-20 DS 1

**Previous Version:**

PEF 20450 / 20470 / 24470 V1.2, Preliminary Data Sheet DS1, 2001-04-04

| Page      | Content                                                                             |

|-----------|-------------------------------------------------------------------------------------|

| 12        | Table 5 updated                                                                     |

| 26        | Chapter 3.4.3 updated, added Figure 9                                               |

| 28        | Chapter 3.7.1 and Chapter 3.7.2 updated                                             |

| 30        | Chapter 4.2 reworked                                                                |

| 49        | Description of Configuration Command Register 1 and 2 (CMD1 and CMD2) updated       |

| <b>57</b> | Description of Interrupt Status Register 1 (ISTA1) reworked                         |

| 58        | Description of Interrupt Error Status Register 1 and 2 (IESTA1 and IESTA2) reworked |

| 60        | Description of Interrupt Error Mask Register 1 and 2 (INTEM1 and INTEM2) reworked   |

| 74        | Chapter 6.2 reworked                                                                |

| 82        | Figure 18 updated                                                                   |

| 85        | Chapter 6.7.3 reworked                                                              |

| 101       | Chapter 7.1 and Table 22 updated                                                    |

| 104       | Table 23 updated                                                                    |

| 110       | Table 27 and Figure 39 updated                                                      |

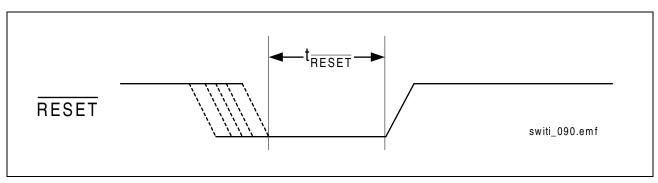

| 112       | Added Chapter, 7.5"Hardware Reset Timing"                                           |

| 115       | Table 32 updated.                                                                   |

|           |                                                                                     |

|           |                                                                                     |

|           |                                                                                     |

|           |                                                                                     |

For questions on technology, delivery and prices please contact the Infineon Technologies Offices in Germany or the Infineon Technologies Companies and Representatives worldwide: see our webpage at http://www.infineon.com

| Table of                                                                                                                                                                                                    | Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Page                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 1<br>1.1<br>1.2<br>1.3<br>1.4                                                                                                                                                                               | Overview Overview of Features Features in Detail Logic Symbol Standard PBX or CO Application                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5<br>6                                             |

| 2.1<br>2.2<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>2.2.5<br>2.2.6                                                                                                                                            | Pin Description Pin Diagrams Pin Definitions and Functions Local Bus Interface (PCM) General Purpose Port Clock Signals JTAG Interface Microprocessor Interface Power Supply                                                                                                                                                                                                                                                                                                                                                                                                               | 11 12 12 12 12 13                                  |

| 3<br>3.1<br>3.2<br>3.3<br>3.3.1<br>3.3.1.1<br>3.3.1.2<br>3.3.1.3<br>3.3.1.4<br>3.3.1.5<br>3.3.1.6<br>3.3.2<br>3.3.3<br>3.3.4<br>3.4.1<br>3.4.2<br>3.4.2.1<br>3.4.2.2<br>3.4.3<br>3.4.4<br>3.5<br>3.6<br>3.7 | Architectural Description Functional Block Diagram Overview of Functional Blocks Switching Factory Switching Modes Minimum and Constant Delay Subchannel Switching Multipoint Switching Broadcast Switching Bidirectional Switching Message Mode Parallel Mode for Local Bus Switching Block Error Handling Analyze Connection and Data Memory Clock Generator and PLL General Overview Analog PLL (APLL) Functional Description Jitter Transfer Function Phase Alignment PLL Synchronization Loops Read SWITI Configuration with Indirect Register Addressing Power-On and Reset Behavior | 15 16 17 17 17 18 18 19 20 21 21 21 22 25 25 27 27 |

| 3.7.1<br>3.7.2<br><b>4</b>                                                                                                                                                                                  | Hardware Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 28                                                 |

| Table of | Contents                                           | Page |

|----------|----------------------------------------------------|------|

| 4.1      | Local Bus Interface (PCM)                          | 29   |

| 4.2      | Data Rate                                          |      |

| 4.3      | Microprocessor Interface                           | 31   |

| 4.3.1    | Intel/Siemens or Motorola Mode                     |      |

| 4.3.2    | De-multiplexed or Multiplexed Mode                 | 31   |

| 4.4      | General Purpose Port (GPIO)                        |      |

| 4.5      | General Purpose Clocks                             | 33   |

| 4.5.1    | Frame Group Outputs                                | 34   |

| 4.5.2    | GPCLK as Clock Outputs                             |      |

| 4.6      | JTAG (Boundary Scan)                               |      |

| 4.6.1    | Boundary Scan                                      | 35   |

| 4.6.2    | Test-Access-Port (TAP)                             | 35   |

| 4.6.3    | TAP Controller                                     | 36   |

| 4.7      | Identification Code via µP Read Access             | 38   |

| 5        | Register Description                               |      |

| 5.1      | Register Overview For 8-Bit Interface              | 40   |

| 5.2      | Detailed Register Description For 8-bit Interface  | 42   |

| 5.3      | Register Overview For 16-Bit Interface             | 67   |

| 5.4      | Detailed Register Description For 16-Bit Interface | 68   |

| 6        | Programming the Device                             |      |

| 6.1      | Read and Write Access                              | 73   |

| 6.2      | Interrupt Handling                                 | 74   |

| 6.3      | Command and Register Overview                      |      |

| 6.4      | Indirect Configuration Register Access             | 81   |

| 6.5      | Initialization Procedure                           |      |

| 6.6      | Clocking Unit                                      | 83   |

| 6.7      | Local Bus (PCM) Line Interface                     | _    |

| 6.7.1    | Standby Command                                    |      |

| 6.7.2    | Determining Clock Rates                            | 84   |

| 6.7.3    | Performing Bit Shifting                            | 85   |

| 6.7.3.1  | Input Bit Shifting                                 | 85   |

| 6.7.3.2  | Output Bit Shifting                                |      |

| 6.8      | Global Clock Signals                               |      |

| 6.8.1    | Framing Groups                                     |      |

| 6.9      | Read Time-Slot Value                               |      |

| 6.10     | Establish Connections                              |      |

| 6.10.1   | Establish 8-bit Connections                        |      |

| 6.10.2   | Subchannel Switching                               |      |

| 6.10.2.1 | Establish 4-bit Connections                        |      |

| 6.10.2.2 | Establish 2-bit Connections                        |      |

| 6.10.2.3 | Establish 1-bit Connections                        |      |

| 6.10.3   | Establish Broadcast Connections                    | 93   |

| Table of                                                                                                       | Contents                                                                                                                                                                                                                                                                                                                                      | Page                                                 |

|----------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| 6.10.4<br>6.10.5<br>6.11<br>6.12<br>6.12.1<br>6.12.2<br>6.12.3<br>6.12.4<br>6.12.5<br>6.12.6<br>6.12.7<br>6.13 | Establish Subchannel Broadcast Connection Establish Multipoint Connection  Send Messages Release Connections Release 8-bit Connections Release 4-bit Connections Release 2-bit Connections Release 1-bit Connections Release Broadcast Connection Release Subchannel Broadcast Connection Release Multipoint Connection Stop Sending Messages | . 95<br>. 96<br>. 97<br>. 97<br>. 97<br>. 98<br>. 99 |

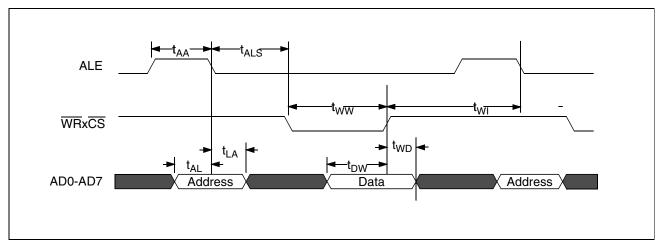

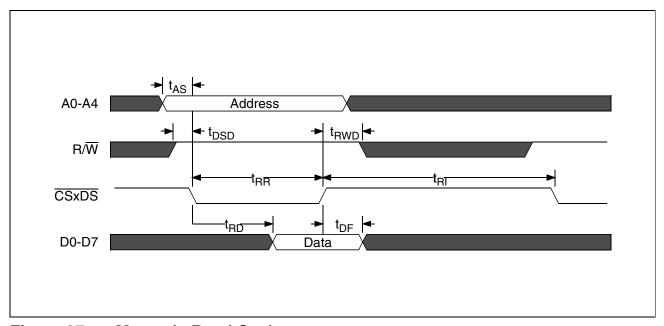

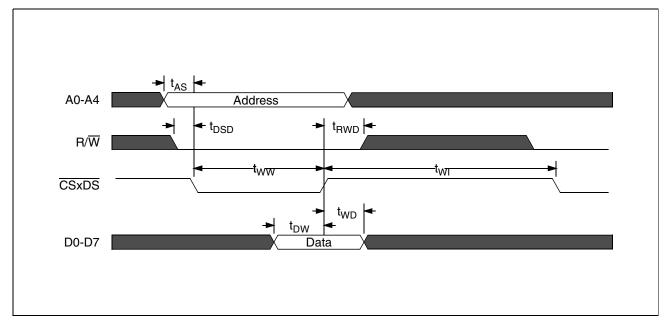

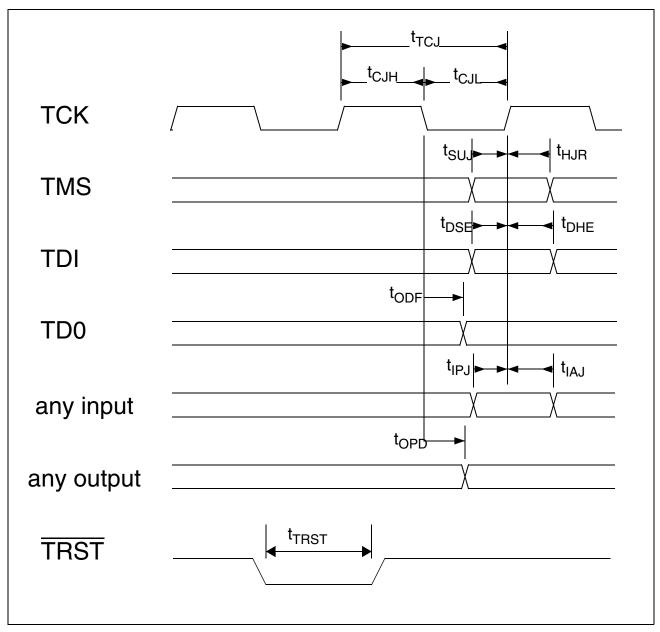

| 7 7.1 7.2 7.3 7.3.1 7.3.2 7.3.3 7.4 7.5                                                                        | Timing Diagrams  PCM Interface Timing  PCM Parallel Mode Timing  Microprocessor Interface Timing  Infineon/Intel Timing in De-Multiplexed Mode  Infineon/Intel Timing in Multiplexed Mode  Motorola Microprocessor Timing  JTAG Interface Timing  Hardware Reset Timing                                                                       | 101<br>104<br>105<br>105<br>106<br>108<br>110        |

| 8<br>8.1<br>8.2<br>8.3<br>8.4<br>8.5<br>8.6                                                                    | Electrical Characteristics  Absolute Maximum Ratings  Operating Range  Crystal Oscillator  DC Characteristics  Capacitances  AC Characteristics                                                                                                                                                                                               | 113<br>113<br>114<br>115<br>115<br>116               |

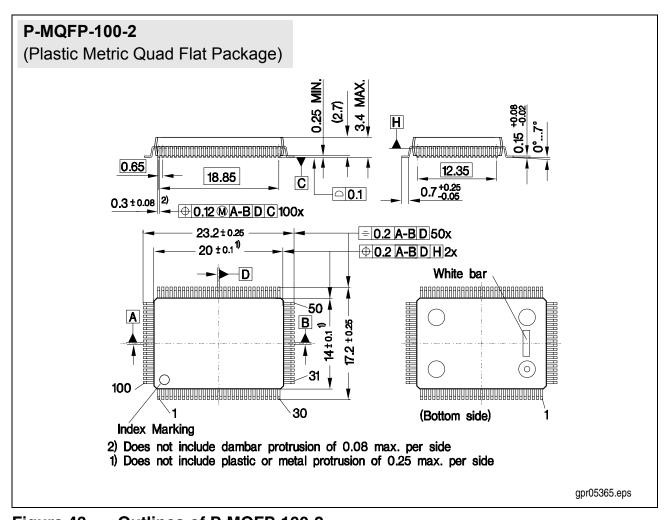

| 9                                                                                                              | Package Outlines                                                                                                                                                                                                                                                                                                                              | 11/                                                  |

| List of Figu | ures                                              | Page |

|--------------|---------------------------------------------------|------|

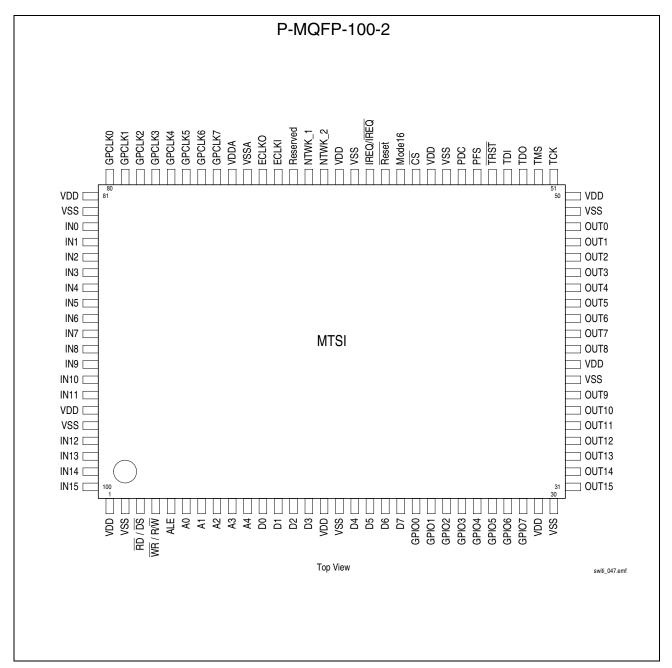

| Figure 1     | Logic Symbol                                      | 9    |

| Figure 2     | Standard PBX or CO Application                    |      |

| Figure 3     | Pin Configuration                                 | 11   |

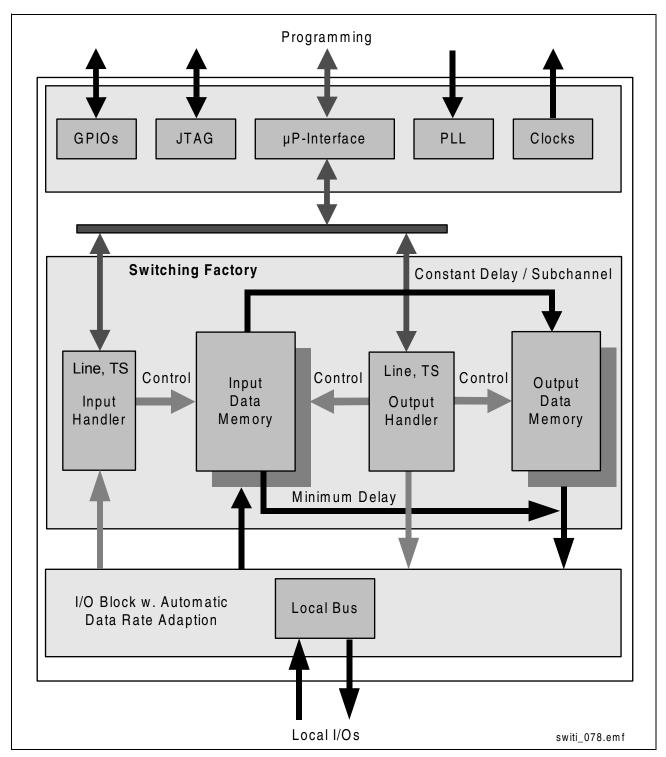

| Figure 4     | Block Diagram                                     |      |

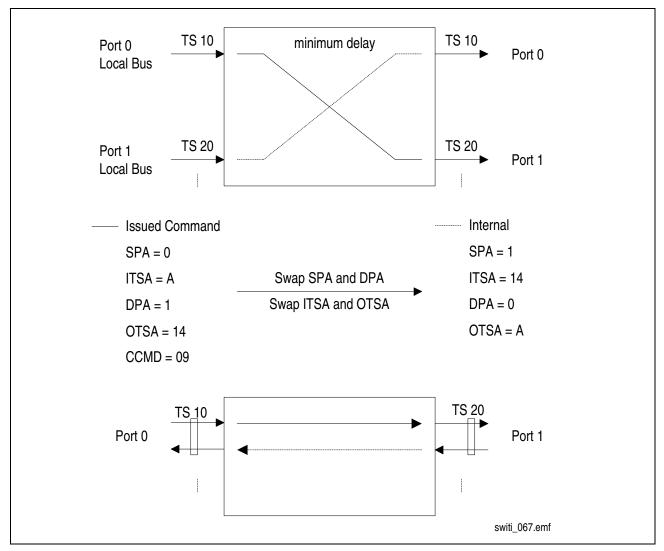

| Figure 5     | Bidirectional Mode                                |      |

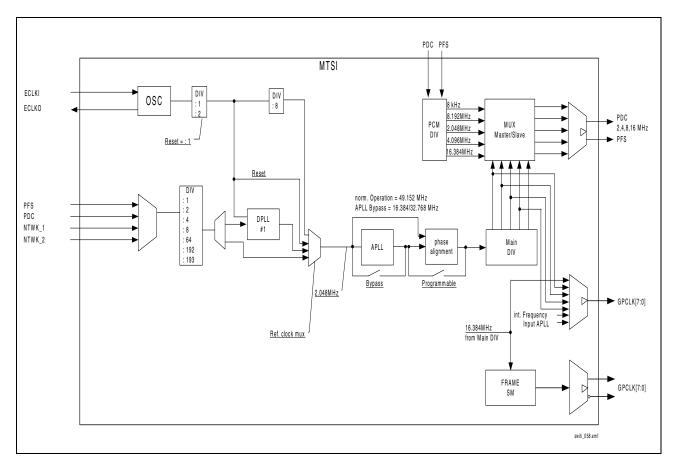

| Figure 6     | SWITI Clock Generator                             | 21   |

| Figure 7     | Block Diagram of APLL                             | 23   |

| Figure 8     | APLL - Jitter Transfer Function                   | 25   |

| Figure 9     | Example of Phase Alignment                        | 26   |

| Figure 10    | PCM Interface Configurations                      | 29   |

| Figure 11    | PCM Bit Shifting                                  | 30   |

| Figure 12    | Multiplexed and in De-multiplexed Bus Mode        | 32   |

| Figure 13    | GPIO Port Configuration Example                   | 33   |

| Figure 14    | Frame Signal Example                              | 34   |

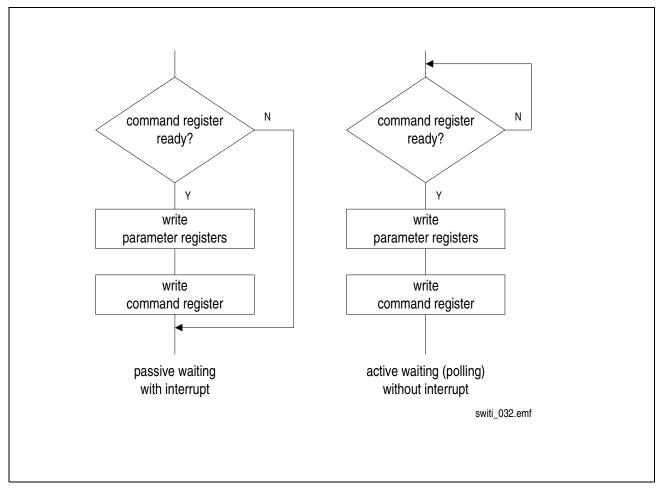

| Figure 15    | Order of Register Access                          | 72   |

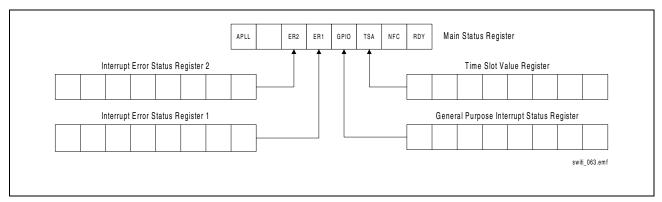

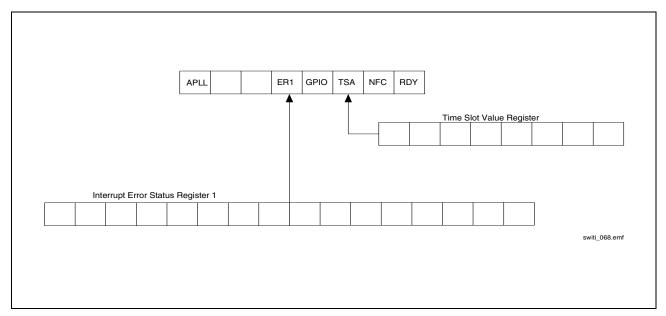

| Figure 16    | 8-bit µP Access Interrupt Structure               | 74   |

| Figure 17    | 16-bit μP Access Interrupt Structure              | 75   |

| Figure 18    | Initialization Procedure after Reset              | 82   |

| Figure 19    | Example: Input Bit Shifting                       | 85   |

| Figure 20    | Example: Output Bit Shifting                      | 86   |

| Figure 21    | Example Framing Groups                            | 87   |

| Figure 22    | Example: 8-bit Connection                         |      |

| Figure 23    | Subchannel Address in Time-Slot                   | 90   |

| Figure 24    | Example: 4-bit Connection                         | 90   |

| Figure 25    | Example: 2-bit Connection                         | 91   |

| Figure 26    | Example: 1-bit Connection                         | 92   |

| Figure 27    | Example: Broadcast Connection                     |      |

| Figure 28    | Example: Subchannel Broadcast Connection          | 94   |

| Figure 29    | Example: Multipoint Connection                    | 95   |

| Figure 30    | Example: Send Message                             |      |

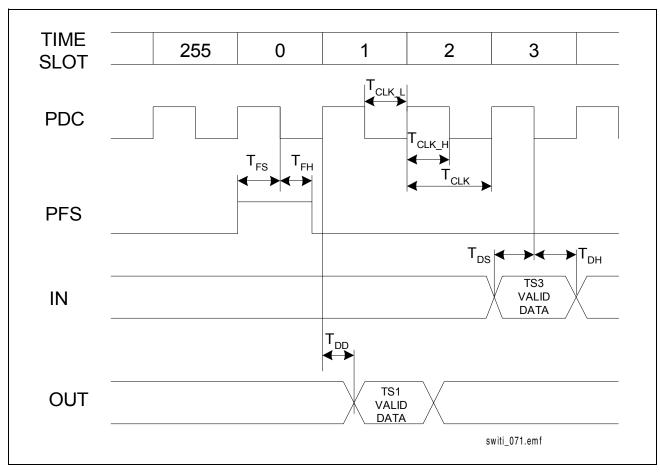

| Figure 31    | PCM Timing                                        |      |

| Figure 32    | Parallel Mode Timing                              |      |

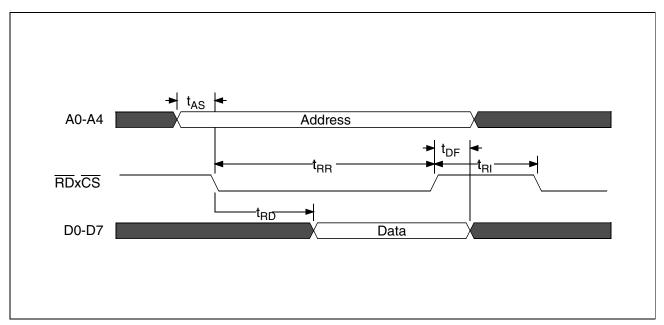

| Figure 33    | Infineon/Intel Read Cycle in De-Multiplexed Mode  |      |

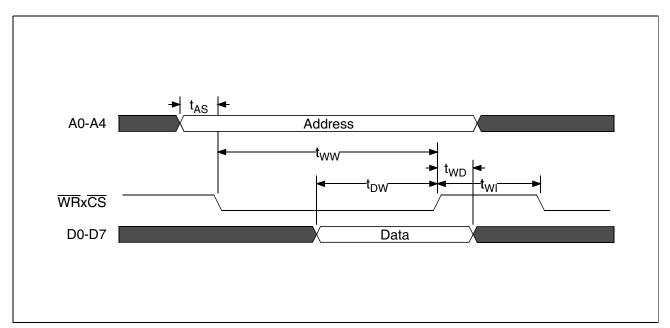

| Figure 34    | Infineon/Intel Write Cycle in De-Multiplexed Mode |      |

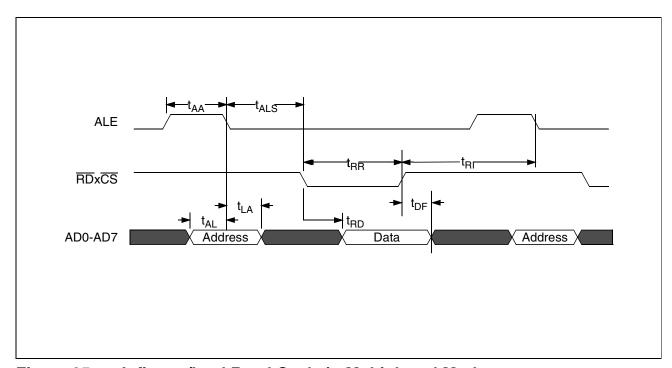

| Figure 35    | Infineon/Intel Read Cycle in Multiplexed Mode     |      |

| Figure 36    | Infineon/Intel Write Cycle in Multiplexed Mode    |      |

| Figure 37    | Motorola Read Cycle                               |      |

| Figure 38    | Motorola Write Cycle                              |      |

| Figure 39    | Boundary Scan Timing                              |      |

| Figure 40    | Hardware Reset Timing                             |      |

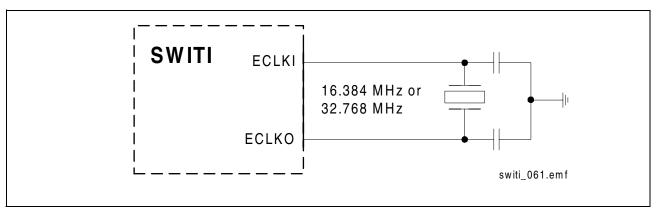

| Figure 41    | External Crystal                                  |      |

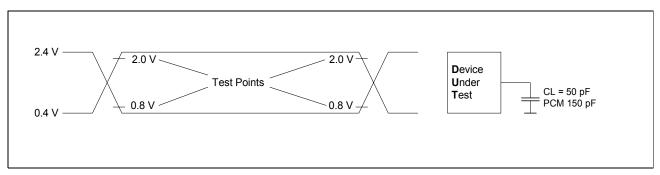

| Figure 42    | I/O Wave Form for AC-Test                         |      |

| Figure 43    | Outlines of P-MQFP-100-2                          | 117  |

# PEF 20450 / 20470 / 24470

| List of Table |                                                    | Page  |

|---------------|----------------------------------------------------|-------|

| Table 1       | Who should read what?                              | 2     |

| Table 2       | SWITI Family Tree                                  | 3     |

| Table 3       | Local Bus Interface                                | 12    |

| Table 4       | GPIO                                               | 12    |

| Table 5       | Clock Pins                                         | 12    |

| Table 6       | JTAG Interface                                     | 13    |

| Table 7       | Microprocessor Interface                           | 13    |

| Table 8       | Power Supply Pins                                  | 14    |

| Table 9       | TAP Controller Instructions                        | 36    |

| Table 10      | Boundary Scan IDCODE                               | 37    |

| Table 11      | IDCODE via µP Read Access                          | 38    |

| Table 12      | Register Overview For 8-Bit Interface              | 40    |

| Table 13      | Value Range for SPA/DPA                            | 41    |

| Table 14      | Value Range for ITSA/OTSA                          | 41    |

| Table 15      | Value Range for SCA                                | 41    |

| Table 16      | Register Overview For 16-Bit Interface             | 67    |

| Table 17      | Affected Registers for Connection Commands         | 76    |

| Table 18      | Affected Registers for Configuration Commands      | 77    |

| Table 19      | Connection Command and Parameter Codes             | 78    |

| Table 20      | Configuration Command 1 and Parameter Codes        | 79    |

| Table 21      | Configuration Command 2 and Parameter Code         | 79    |

| Table 22      | PCM Timing                                         | . 102 |

| Table 23      | PCM Parallel Mode Timing                           | . 104 |

| Table 24      | Infineon/Intel Timing in De-Multiplexed Mode       | . 105 |

| Table 25      | Infineon/Intel Timing in Multiplexed Mode          | . 107 |

| Table 26      | Motorola Timing                                    | . 108 |

| Table 27      | JTAG Interface Timing                              | . 110 |

| Table 28      | Hardware Reset Timing                              | . 112 |

| Table 29      | Absolute Maximum Ratings                           | . 113 |

| Table 30      | Operating Range                                    | . 113 |

| Table 31      | External Capacitances for Crystal (Recommendation) | . 114 |

| Table 32      | DC Characteristics                                 | . 115 |

| Table 33      | Input/Output Capacitances                          | . 115 |

# **Preface**

The Switching IC (SWITI) is a family of switching devices for a wide area of telecommunication and data communication applications. This document provides complete reference information according to chip interfaces, programming, internal architecture and applications.

# **Organization of this Document**

This Preliminary Data Sheet is divided into 9 chapters. It is organized as follows:

# Chapter 1, Overview

Gives a general description of the product and its family, lists the key features, and presents some typical applications.

# Chapter 2, Pin Description

Lists pin locations with associated signals, categorizes signals according to function, and describes signals.

# Chapter 3, Description of Interfaces

Rough overview of the internal architecture.

# Chapter 4, Description of Interfaces

Short introduction of used interfaces.

# Chapter 5, Register Description

Gives information about all registers accessible via the microprocessor interface according to address, short name, access, reset value and value range.

### Chapter 6. Programming the Device

Gives a variety of examples how to programm the device, lists all available command and parameter values.

# • Chapter 7, Timing Diagrams

Contains timing diagrams.

# Chapter 8, Electrical Characteristics

Specification of the electrical parameters.

# Chapter 9, Package Outlines

Outlines of the available packages (P-MQFP-100-2).

# Table 1 Who should read what?

| Addressed Person | Relevant Chapters |

|------------------|-------------------|

| Programmer       | 3, 5, 6           |

| Board Designer   | 2, 3, 4, 7, 8, 9  |

# 1 Overview

The new switching family, called SWITI, provides a complete and cost-effective solution for all switching systems. The family is divided in two sub-families, the MTSI family and the HTSI family. The Preliminary Data Sheet describes the functionality and characteristic of the MTSI devices.

The devices can be used in today's switching applications, e.g. conventional PBXs and central offices, as well as in H.100/H.110 applications (only the HTSI family), which are the key to high performing CTI- and Voice-over-IP-applications, one of the most important future technologies in telecommunications.

The main requirements of today's switching applications are met by the following features:

- Constant delay e.g. to support wide band data switching, or channel bundling

- Bit switching/subchannel switching to support applications such as mobile base stations, DECT, computer telephony

In addition, the SWITI family provides new features to ensure a broad range of configurations to make it possible to adapt the device to all switching applications:

- A compliant H.100/H.110 interface (HTSI)

- 8-channel stream-to-stream switching capability (HTSI)

- · Message mode, which allows to assign a preset value to any output time-slot

- GPIO (General Purpose I/O) port, which is controlled from the external μP

**SWITI family.** The SWITI family consists of 6 ICs with different switching capacities. The possible configurations are shown in **Table 2**. The HTSI versions provide an additional H.100 / H.110 interface, while the MTSIs are standard switching devices. All devices can be programmed easily, thus helping the designer/programmer to integrate the device into his application comfortably.

Table 2 SWITI Family Tree

| Name             | Package     | Sales<br>code       | Connec-<br>tions | Local bus IN/OUT | H-Bus IO |

|------------------|-------------|---------------------|------------------|------------------|----------|

| HTSI-XL (H-Mode) | P-BGA-217-1 | PEF24471<br>HTSI-XL | 2048             | 16/16            | 32       |

| HTSI-XL (M-Mode) |             | PEF24471<br>HTSI-XL |                  | 32/32            | -        |

| HTSI-L (H-Mode)  | P-BGA-217-1 | PEF20471<br>HTSI-L  | 1024             | 16/16            | 32       |

| HTSI-L (M-Mode)  |             | PEF20471<br>HTSI-L  |                  | 32/32            | -        |

3

# Table 2 SWITI Family Tree (cont'd)

| Name          | Package      | Sales<br>code       | Connec-<br>tions | Local bus IN/OUT | H-Bus IO |

|---------------|--------------|---------------------|------------------|------------------|----------|

| HTSI (H-Mode) | P-BGA-217-1  | PEF20451<br>HTSI    | 512              | 16/16            | 32       |

| HTSI (M-Mode) |              | PEF20451<br>HTSI    |                  | 32/32            | -        |

| MTSI-XL       | P-MQFP-100-2 | PEF24470<br>MTSI-XL | 2048             | 16/16            | -        |

| MTSI-L        | P-MQFP-100-2 | PEF20470<br>MTSI-L  | 1024             | 16/16            | -        |

| MTSI          | P-MQFP-100-2 | PEF20450<br>MTSI    | 512              | 16/16            | -        |

# Switching IC SWITI

### PEF 20450 / 20470 / 24470

Version 1.3 CMOS

# 1.1 Overview of Features

### General

- Switching capacity of 512, 1024, or up to 2048 connections of different types between different buses

- Programmable data rates of 2.048 Mbit/s, 4.096 Mbit/s, 8.192 Mbit/s, and 16.384 Mbit/s on per stream basis

- Constant delay or minimum delay programmable on per connection basis

- Subchannel switching ability of 1-bit, 2-bit, 4-bit wide time-slots

- Programmable clock shift for local bus

- Automatic data rate adaption

- Optional 8-bit parallel input and/or 8-bit parallel output for first 8 lines of local bus

- Broadcast capabilities

- Multipoint switching ability

- · Read and write access to all time-slots

- Message mode (time-slot write access)

- Programmable framing group

- GPIO port

- 8-bit µP-interface supports both Intel and Motorola mode

- Optional 16-bit µP interface mode (instead of GPIO port)

- On chip PLL for PCM bus clock operation (master/slave)

- JTAG interface

- Boundary scan according to IEEE 1149.1

- 3.3 V power supply

- 5 V tolerant inputs/outputs

| P-MQFP-100-2 |  |

|--------------|--|

| Туре                      | Package      |

|---------------------------|--------------|

| PEF 20450 / 20470 / 24470 | P-MQFP-100-2 |

### 1.2 Features in Detail

### **Flexible Data Rates**

Each input and each output line of the local bus is programmable to operate at different data rates. The possible data rates are 2.048 Mbit/s, 4.096 Mbit/s, 8.192 Mbit/s, and 16.384 Mbit/s.

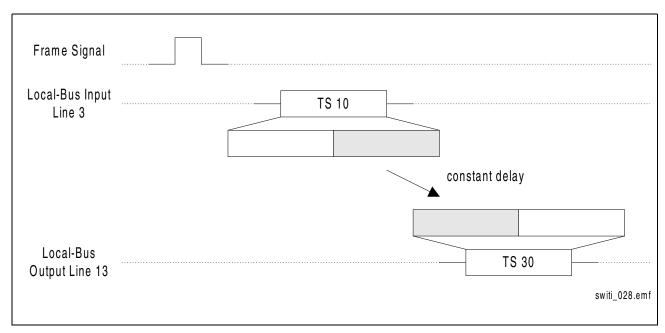

# **Constant and Minimum Delay**

Each connection independent of the addressed buses can be determined to be a constant delay or minimum delay connection. Constant delay means that any input time-slot or subchannel is available on the programmed output after 2 frames. Minimum delay means that the time-slot or subchannel appears at the output as soon as possible. The minimum delay depends on the chosen connections and the possible range is between 0 and 2 frames.

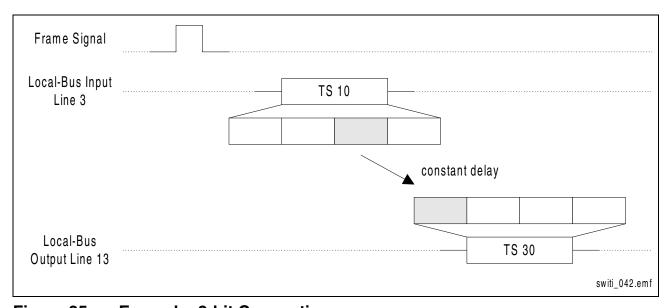

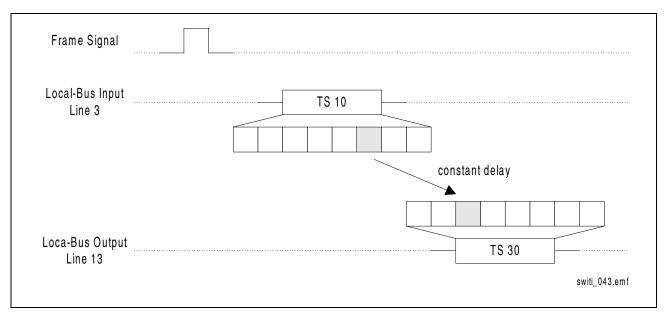

# **Subchannel Switching**

Each connection can be a 1-bit, 2-bit, 4-bit, or 8-bit connection. Subchannel switching has a constant delay of 2 frames. Subchannel switching is supported only for data rate of 2.048 Mbit/s, 4.096 Mbit/s and 8.192 Mbit/s.

### **Programmable Clock Shift**

The position of time-slot 0 of each local bus input line can be programmed within the time-slot before and after the PFS rising edge in half bit steps. Also the position of time-slot 0 of all local bus output lines can be programmed within the first time-slot after the PFS rising edge.

# **Automatic Data Rate Adaption**

Connections are also possible between lines operating at different data rates. The programmer just specifies input and output line, time-slot, and if necessary, the subchannel.

### **Parallel Mode**

The first 8 local bus input and output lines can be configured to one parallel input or output port respectively. In serial mode a time-slot is determined by 8 consecutive data clock cycles according to each line. In parallel mode a time-slot is determined by 1 data clock cycle according to the first 8 lines.

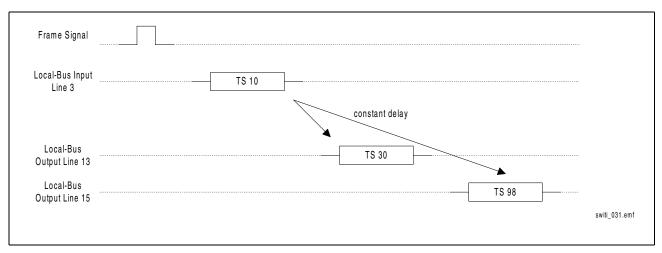

### **Broadcast**

With this feature it is possible to distribute one incoming time-slot to different output time-slots.

# Multipoint

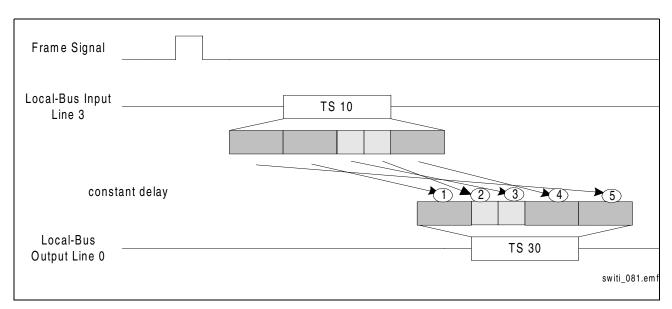

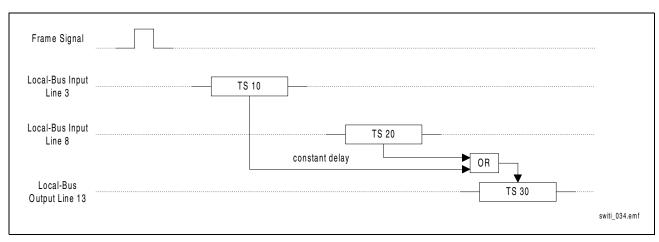

Multipoint connections can be seen as the opposite of broadcast connections. Here it is possible to generate one output time-slot consisting of several input time-slots. The specified input time-slots are logically AND or OR connected (selectable) and have a constant delay of 2 frames.

### **Read Access**

The programmer has access to any input time-slot. After issuing an appropriate command the arrival of the time-slot will be reported by interrupt. The value can be read from a dedicated register. For every read request the command has to be issued again.

# **Message Mode (Write Access)**

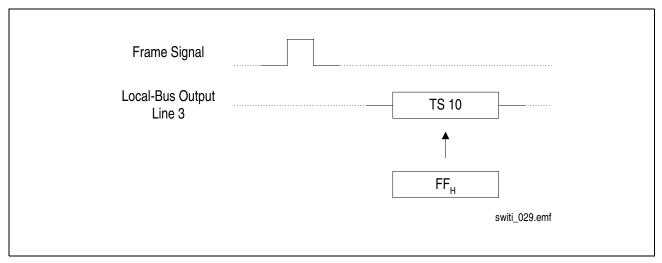

This feature allows a constant value to be sent to any given output time-slot.

# **Framing Group**

It is possible to specify up to 8 different framing signals of 8 kHz. The position of the rising edge and the pulse width can be programmed for each signal. The reference frame is determined by the PFS signal. The pulse parameters are programmed in half step resolution according to a 16.384 MHz clock.

# **General Purpose Clocks**

All 8 GPCLK lines can be configured as individual clock outputs with 8 kHz, 2.048 MHz, 4.096 MHz, 8.192 MHz, 16.384 MHz and for test purposes with the internal frequency or the input frequency of the analog PLL (APLL).

### **GPIO Port**

Each line of the general purpose input/output port can be configured to be either input or output. According to an input an edge causes an interrupt. The outputs can be influenced by write access via the microprocessor interface. Thus the user has the possibility to observe and influence additional signals for his application.

# **Microprocessor Interface**

All devices provide a standard 8-bit microprocessor interface operating in either Intel or Motorola mode. Optionally it is possible to configure the GPIO port as additional data lines to provide a 16-bit microprocessor interface. The use of the 16-bit µP interface

reduces the number of write cycles required to configure a connection from 7 (in case of 8-bit µP interface) to 3 write cycles.

# **Input/Output Tolerance**

The MTSI can be used in a 5 V environment. Inputs and outputs are 3.3 V and 5 V tolerant. The outputs have TTL level driving capability.

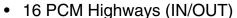

# 1.3 Logic Symbol

The MTSI is a pure PCM switch and provides 16 PCM input lines and 16 PCM output lines.

Figure 1 Logic Symbol

# 1.4 Standard PBX or CO Application

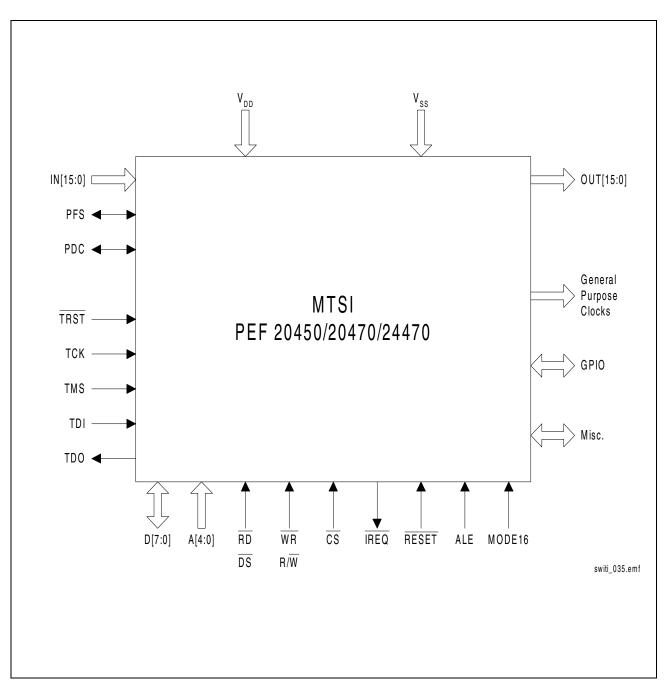

The MTSI or the HTSI in M-Mode can be used, just as the MTSC or MTSL, in standard private branch exchange or central office applications (**Figure 2**), e.g. in the switching network.

Figure 2 Standard PBX or CO Application

# PRELIMINARY Pin Description

# 2 Pin Description

The pin description gives an overview of the pin numbers, names, direction, position and function ordered by the different interfaces.

Note: All unused input or I/O pins should be connected to  $V_{SS}$  to avoid leakage current.

# 2.1 Pin Diagrams

Figure 3 Pin Configuration

# PRELIMINARY Pin Description

# 2.2 Pin Definitions and Functions

# 2.2.1 Local Bus Interface (PCM)

Table 3 Local Bus Interface

| Pin No.          | Symbol                  | In (I)<br>Out (O) | Function                                                                  | Reset<br>Behavior |

|------------------|-------------------------|-------------------|---------------------------------------------------------------------------|-------------------|

| 56               | PFS                     | I/O               | PCM Frame Synchronization Clock of 8 kHz                                  | High Z            |

| 57               | PDC                     | I/O               | PCM Data Clock of 2.048 Mbit/s, 4.096 Mbit/s, 8.192 Mbit/s, 16.384 Mbit/s | High Z            |

| 100-97,<br>94-83 | IN[15:0] <sup>1)</sup>  | I                 | PCM Receive Data Port 15 to 0                                             |                   |

| 31-37,<br>40-48  | OUT[15:0] <sup>2)</sup> | 0                 | PCM Transmit Data Port 15 to 0                                            | High Z            |

<sup>1) 100</sup> is IN15, 99 is IN14, 98 is IN13..

# 2.2.2 General Purpose Port

# Table 4 GPIO

| Pin No. | Symbol                  | In (I)<br>Out (O) | Function                                                   | Reset<br>Behavior |

|---------|-------------------------|-------------------|------------------------------------------------------------|-------------------|

| 28-21   | GPIO[7:0] <sup>1)</sup> | I/O               | General Purpose I/O port (only if 8-bit μP interface used) | Input             |

|         | D[15:8]                 |                   | Upper 8 bit of 16-bit μP interface                         |                   |

<sup>1) 28</sup> is GPIO7, 27 is GPIO6, 26 is GPIO5..

# 2.2.3 Clock Signals

Table 5 Clock Pins

| Pin No. | Symbol     | In (I)<br>Out (O) | Function                                                                                                      | Reset<br>Behavior |

|---------|------------|-------------------|---------------------------------------------------------------------------------------------------------------|-------------------|

| 69      | ECLKI      | I                 | External Crystal Input of 16.384 MHz, or 32.768 MHz<br>External Oscillator Input of 16.384 MHz, or 32.768 MHz |                   |

| 70      | ECLKO      | 0                 | External Crystal Output of 16.384 MHz, or 32.768 MHz                                                          |                   |

| 73-80   | GPCLK[7:0] | 0                 | General Purpose Clock Output (Framing Signals)                                                                | High Z            |

<sup>&</sup>lt;sup>2)</sup> 31 is OUT15, 32 is OUT14, 33 is OUT13..

# **Pin Description**

Table 5Clock Pins (cont'd)

| Pin No. | Symbol | In (I)<br>Out (O) | Function                                                                                                                                                         | Reset<br>Behavior |

|---------|--------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 67      | NTWK_1 | I                 | Primary Network Timing Reference Input<br>Optionally the PLL can be synchronized to this input which<br>can be 8 kHz, 512 kHz, 1.536 MHz, 1.544 MHz, 2.048 MHz   |                   |

| 66      | NTWK_2 | I                 | Secondary Network Timing Reference Input<br>Optionally the PLL can be synchronized to this input which<br>can be 8 kHz, 512 kHz, 1.536 MHz, 1.544 MHz, 2.048 MHz |                   |

<sup>1) 73</sup> is GPCLK7, 74 is GPCLK6, 75 is GPCLK5...

# 2.2.4 JTAG Interface

Table 6 JTAG Interface

| Pin No. | Symbol | In (I)<br>Out (O) | Function                                                                                                           | Reset<br>Behavior |

|---------|--------|-------------------|--------------------------------------------------------------------------------------------------------------------|-------------------|

| 51      | TCK    | I                 | Test Clock<br>Single rate test data clock.                                                                         |                   |

| 52      | TMS    | I                 | Test Mode Select A '0' to '1' transition on this pin is required to step through the TAP controller state machine. |                   |

| 55      | TRST   | I                 | Test Reset Resets the TAP controller state machine (asynchronous reset).                                           |                   |

| 53      | TDO    | 0                 | Test Data Out In the appropriate TAP controller state test data or a instruction is shifted out via this line.     | High Z            |

| 54      | TDI    | I                 | Test Data Input In the appropriate TAP controller state test data or a instruction is shifted in via this line.    |                   |

# 2.2.5 Microprocessor Interface

Table 7

Microprocessor Interface

| Pin No. | Symbol    | In (I)<br>Out (O) | Function                                                                                                                                                                             | Reset<br>Behavior |

|---------|-----------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 60      | <u>CS</u> | I                 | Chip Select Active low. A "low" on this line selects all registers for read/write operations.                                                                                        |                   |

| 3       | RD        | I                 | Read (Intel/Infineon Mode) Indicates a read access.                                                                                                                                  |                   |

|         | DS        |                   | Data Strobe (Motorola Mode) During a read cycle, DS indicates that the device should place valid data on the bus. During a write access, DS indicates that valid data is on the bus. |                   |

# **Pin Description**

Table 7

Microprocessor Interface (cont'd)

| Pin No.         | Symbol               | In (I)<br>Out (O) | Function                                                                                                                                                                                                                                                                              | Reset<br>Behavior |

|-----------------|----------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| 4               | WR                   | I                 | Write (Intel/Infineon Mode) Indicates a write access.                                                                                                                                                                                                                                 |                   |

|                 | R/W                  |                   | Read/Write (Motorola Mode) Indicates the direction of the data transfer on the bus.                                                                                                                                                                                                   |                   |

| 5               | ALE                  | I                 | Address Latch Enable Controls the on-chip address latch in multiplexed bus mode. While ALE is 'high', the latch is transparent. The falling edge latches the current address. ALE is also evaluated to determine the bus mode (ALE fix 'low' = Motorola, fix 'high' = Intel/Infineon) |                   |

| 61              | MODE16               | I                 | Microprocessor Bus 8/16-Bit Interface Selection ('low' = 8 bit, 'high' = 16 bit)                                                                                                                                                                                                      |                   |

| 63              | IREQ/<br>IREQ        | O<br>OD           | Interrupt Request This pin is programmable to push/pull (active high or low) or open-drain. This signal is activated when SWITI requests an µP interrupt. When operated in open drain mode, multiple interrupt sources may be connected.                                              | High Z            |

| 10-6            | A[4:0] <sup>1)</sup> | I                 | Address Bus<br>When operated in address/data multiplex mode, the<br>address pins are externally connected to the D bus.                                                                                                                                                               |                   |

| 20-17,<br>14-11 | D[7:0] <sup>2)</sup> | I/O               | Data bus                                                                                                                                                                                                                                                                              |                   |

| 62              | RESET                | I                 | System Reset<br>SWITI is forced to go into reset state.                                                                                                                                                                                                                               |                   |

<sup>1) 10</sup> is A4, 9 is A3, 8 is A2...

# 2.2.6 Power Supply

Table 8 Power Supply Pins

| •••                              |                  |                   |                                                 |  |  |  |

|----------------------------------|------------------|-------------------|-------------------------------------------------|--|--|--|

| Pin No.                          | Symbol           | In (I)<br>Out (O) | Function                                        |  |  |  |

| 1,15, 29,39,<br>50,59, 65,81, 95 | V <sub>DD</sub>  | I                 | Power Supply 3.3 V                              |  |  |  |

| 2,16, 30,38,<br>49,58, 64,82, 96 | V <sub>SS</sub>  | I                 | Digital Ground (0 V)                            |  |  |  |

| 72                               | V <sub>DDA</sub> | I                 | Power Supply Analog Logic 3.3 V<br>Used for PLL |  |  |  |

| 71                               | V <sub>SSA</sub> | I                 | Analog Ground (0 V)                             |  |  |  |

| 68                               | R                |                   | Reserved. Must be connected to ground           |  |  |  |

<sup>&</sup>lt;sup>2)</sup> 20 is D7, 19 is D6, 18 is D5..

# **Architectural Description**

# 3 Architectural Description

The following sections give a short overview of the functionality of the SWITI.

# 3.1 Functional Block Diagram

Figure 4 Block Diagram

# **Architectural Description**

### 3.2 Overview of Functional Blocks

# **Switching Factory**

The switching factory is responsible for transferring and handling the incoming data streams to the assigned output channels and time-slots. The block includes a 512, 1024, or 2048 byte input and output data memory as well as an input and output connection memory.

# Local bus I/O Block

The block is designed to handle the conversion of the data provided via the switching block and the external local bus (PCM) interface. It performs the PCM timing, the data rate selection and the tristate control.

# **Microprocessor Interface Block**

A standard 8-bit multiplexed or de-multiplexed  $\mu P$  interface is provided, compatible to Intel/Infineon Tech. (e.g. 80386EX, C166) and Motorola (e.g. 68040, 68340, 68360, 801) bus systems. If the GPIO port is not needed it can be used to provide a 16-bit  $\mu P$  interface.

### **GPIO Block**

This block supports up to 8 external port lines each one configurable as input or output. A change on an input line may cause an interrupt (if not masked). The user has access to the port configuration and information via the appropriate registers of the µP interface.

### **PLL and Clock Block**

The PLL generates all frequencies supporting the local bus (PCM). The internal phase-locked loop (PLL) generates all bus frequencies synchronized to a selected reference signal. The output frequency tolerance is equal to the input frequency tolerance. The PLL operates from a 16.384 MHz, or 32.768 MHz external crystal, oscillator.

# **Architectural Description**

# 3.3 Switching Factory

As shown in **Figure 4** the switching factory comprises the input/output data memory and the input/output data handler with the programmed connections. The I/O controller handles all lines operating at the same or different data rate. To establish a connection the user must only program the source line with time-slot and the destination line with the time-slot. The internal controller (data handler) writes the connection in a connection descriptor list and stores this list in the connection data handler. The programming procedure is described in **Chapter 6**. The incoming time-slot will be stored in the input data memory controlled by the input handler. The output handler controls the constant, minimum delay and subchannel switching.

# 3.3.1 Switching Modes

The SWITI family supports a various number of switching modes. All modes are described in the following chapters.

# 3.3.1.1 Minimum and Constant Delay

Each connection independent of the addressed buses can be determined to be a constant delay or minimum delay connection. Constant delay means that any input time-slot or subchannel is available on the programmed output after 2 frames. Minimum delay means that the time-slot appears at the output as soon as possible. The minimum delay depends on the chosen connections and the possible range is between 0 and 2 frames, up to 3 frames in rare cases.

An application note which describes the possible connection and minimum delays is available.

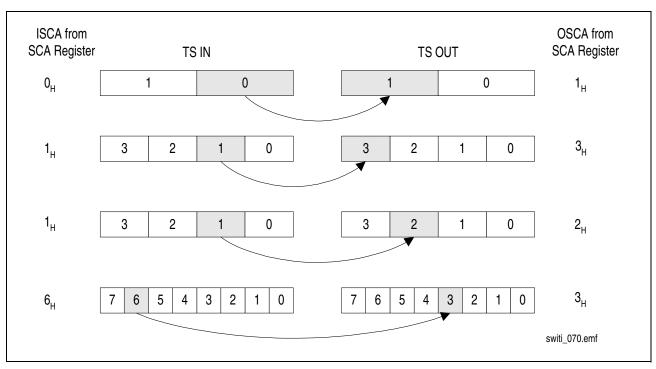

# 3.3.1.2 Subchannel Switching

Subchannel switching has a constant delay of 2 frames. Every connection can be 1-bit, 2-bit, 4-bit, or normal 8-bit connection. It is possible to combine every kind of subchannel connection, e.g. two 1-bit time-slots with one 4-bit time-slot to one output time-slot. Please refer to **Chapter 6.10.2** for a detailed description about the programming.

# 3.3.1.3 Multipoint Switching

As described in the overview the multipoint-switching allows to switch several input time-slots to one output time-slot. All input data are logical AND or OR connected. This mode is selectable with the multipoint connection command. The setup (logical AND or OR) for the last connection determines all other previous programmed multipoint connections. Multipoint switching has always a constant delay. Subchannel switching is not supported.

# **Architectural Description**

# 3.3.1.4 Broadcast Switching

Broadcast switching allows to distribute one incoming time-slot to different output time-slots. The input and output mechanism is the same as the normal constant delay connection mode with subchannel switching. Minimum delay is also supported without subchannel switching.

A table with the possible connections and minimum delays will be provided.

The broadcast connection is programmed in the same way as a normal connection. The output time-slots can be released with the disconnect part of broadcast command. The last connection must be released with the normal disconnect command.

### **Subchannel Broadcast**

It is possible to program one input time-slot as broadcast subchannel connections. That means the bits from the input time-slot are used in several broadcast connections related to one ore more output time-slots.

The output time-slots must be released with the disconnect part of broadcast command. The last subchannel connection must be released with the normal disconnect command. (Please refer to **Chapter 6.10.4** for an example)

# 3.3.1.5 Bidirectional Switching

Bidirectional switching allows to install very easily a symmetrical bidirectional connection (Figure 5). The input and output mechanism is the same as the normal constant delay or minimum delay connection. The time to program a bidirectional connection is twice as the time to program a normal connection since the internal state machine has to calculate the belonging connection. There is a special command to program a bidirectional connection. A bidirectional connection can only be programmed on an available time-slot and input/output line.

# **Architectural Description**

Figure 5 Bidirectional Mode

# 3.3.1.6 Message Mode

The message mode allows to send a predefined 8-bit data value in a defined time-slot on a dedicated destination port. Message mode is started or stopped via register CCMD. The data value to be send is predefined in register MV. The time-slot and the destination port is is defined in register OTSA and register DPA.

### 3.3.2 Parallel Mode for Local Bus

The parallel mode can be set with the 'set parallel mode' command in the configuration command register. This command set the first 8 input lines and the first 8 output lines of the local bus as parallel bus. If the parallel mode is enabled all included lines will be set to 2.048 Mbit/s automatically. If the parallel mode is disabled all lines will keep the data rate of 2.048 Mbit/s until a new data rate will be programmed for the selected line.

# **Architectural Description**

The internal S/P-converter is bypassed. The 8 bit data stream per time-slot is distributed on 8 data lines, one bit for every line. The least significant bit is assigned to line 0 and the most significant bit is assigned to line 7. To program a connection line 0 must be used for this special parallel data port. The bit shift value must only be programmed for port 0 and this value will be assigned to the other 7 ports automatically. The initialize sequence is described in **Chapter 6**.

The switching data handling is the same as the data handling for constant delay or minimum delay mode. A timing diagram is provided in the timing diagram chapter ("PCM Parallel Mode Timing" on page 104.).

# 3.3.3 Switching Block Error Handling

The normal procedure to establish a connection is explained in **Chapter 6**. The way to program a new connection for a specific time-slot and data line is to release the connection and to program the new connection. The SWITI switching concept provides an internal error handling to detect errors in the switching chain caused by a programming error. A programming error can occur because of noises on the data lines, software errors, etc.

A programming error is defined as follows:

- if a non existing connection (minimum, constant delay, or message) will be released.

- or if an existing minimum delay connection will be established.

If a programming error or a connection memory overflow is detected the interrupt bit CON in the **IESTA2** register will be set. In this case the last connection which has been tried to establish or to release is not valid. The operation of the switching device is not affected and will be continued without any restrictions.

For debug purposes the SWITI has the capability to write out the content of the complete connection memory and data memory via the microprocessor interface. This procedure is described in **Chapter 3.3.4**.

It is recommended to track all established and connections with the specific customer application software. For debug purpose it is useful to compare the contents of the switching memory with the virtual connections in the application software.

# 3.3.4 Analyze Connection and Data Memory

With the special command "memory dump enable" in the connection command register (CCMD) it is possible to read the complete memory in a defined sequence from the CON register with a 8-bit  $\mu P$  access. This feature can be used only for analyze purposes.

The command disables the complete switching function as far as all data lines are set to high impedance. If the command is set and after the specific recovery time (200 ns) the connection chain and data memory can be read sequentially by a  $\mu P$  access to the CON register. The internal controller writes the next 8-bit memory data in the CON register if

# **Architectural Description**

the  $\mu P$  read access is finished. That means there is a specific recovery time for the  $\mu P$  to the next CON read access.

The internal memory dump controller reads the present memory contents of the input chain memory, data memory and output chain memory. During the memory dump the internal state machine will loose the synchronization with the external frame structure. Therefore a software reset must be issued and the device must be programmed again, except the clock configuration.

Infineon Technologies provides a software driver to recalculate the chain and to recover the current connections.

# 3.4 Clock Generator and PLL

### 3.4.1 General Overview

The following figure gives a overview about the clock generator with the integrated PLL.

Figure 6 SWITI Clock Generator

The SWITI clock generator provides all necessary clock signals for the MTSI local bus (PCM) interface. Since the device is a PCM clock master capable device there is one digital PLL which can be locked to different network reference signals (< 2.048 MHz).

# **Architectural Description**

The digital PLL synchronizes the external crystal or oscillator to the selected reference clock. The digital PLL (DPLL) will be bypassed if the selected reference signal is >= 2.048 MHz. The input signal for the analog PLL (APLL) is 2.048 MHz in normal operation mode. The APLL is used for multiplying the 2.048 MHz clock into a 49.152 MHz clock and to generate all clock signals for the PCM, and general purpose clock signals.

The SWITI has an on-chip oscillator which allows the user to connect an external 16.384 MHz or 32.768 MHz crystal. Instead of using the crystal it is possible to assign a 16.384 MHz, or 32.768 MHz oscillator to the ECLKI pin.

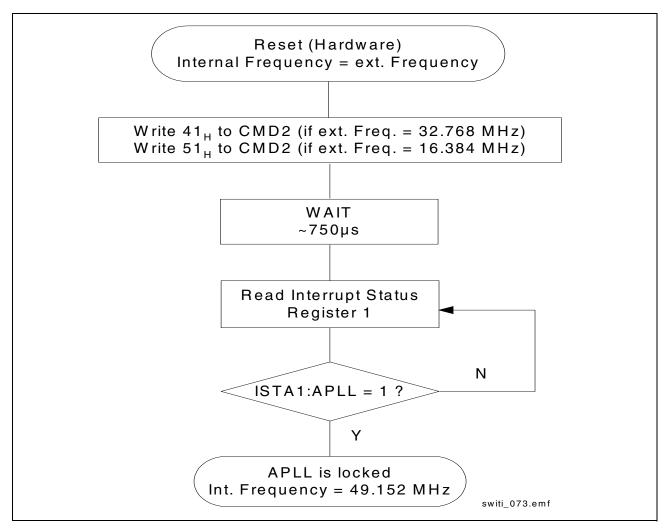

After the power-on or hardware reset the APLL is bypassed. The APLL will be synchronized (after approximately 750 µs) to the external crystal or external oscillator if the command 'set external frequency' is set. This command must be used otherwise the internal working frequency is equal to the external input frequency and the SWITI will not work properly. If the APLL is locked the status bit 'APLL' in the ISTA1 register will be set.

Note: After the reset it is necessary to program the correct crystal or oscillator value as first programming step. Otherwise the operation frequency for the SWITI is not correct.

# 3.4.2 Analog PLL (APLL)

### **Features**

- Low cycle-to-cycle jitter < 1 ns</li>

- Natural frequency f<sub>a</sub> = 15 kHz

- Damping factor = 0.7

- Input Frequency = 2.048 MHz in any case

- Output Frequency = 49.152 MHz, duty-cycle = 50 %

- Rule behavior = change of output frequency in range of 0 ±10% in response to changes of input frequency

- phase slope of output frequency equal to phase slope of input frequency

Note: It is necessary to provide a "noise free" analog power ( $V_{DDA}/V_{SSA}$ ) to reduce the internal jitter of the APLL. These pins must be decoupled from the digital power (VDD/VSS), see also the available Application Note "Layout Notes".

# **Architectural Description**

# 3.4.2.1 Functional Description

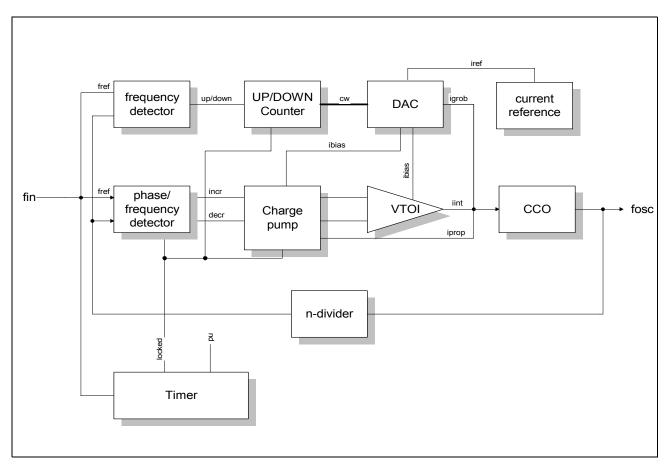

Figure 7 Block Diagram of APLL

The value of the output frequency depends of the programming of the n-divider. The chosen output frequency for the SWITI is 49.152 MHz and the input frequency is 2.048 MHz.

The macro consists of a digital and an analog PLL which are working together. During start-up only the digital one is enabled and makes a coarse adjustment, so that the technology dependency of the circuit is compensated. Afterwards the digital PLL is disabled again and the analog one is switched on for normal operation.

The digital PLL is of first order and consists of a frequency detector (FD), an up/down counter, a digital-to-analog converter (DAC) and a current controlled oscillator (CCO). The FD detects any frequency difference between the reference clock (fref: input clock fin = 2.048 MHz) and the divided oscillator clock. The output signal controls the counter. If the reference frequency is higher than the divided oscillator frequency the counter is increased. The counter output drives a current steering DAC which controls the input current of the internal oscillator. Its current rises and the output frequency increases until both frequencies are equal.

# **Architectural Description**

The digital PLL is enabled after reset or power up and is disabled after 750  $\mu$ s (lock time of PLL). The counter keeps its value and the DAC output current **irough** is constant until the digital PLL is reseted.

The second order analog PLL consists of a phase/frequency detector (PFD), a charge pump (CP), a loop filter and the CCO.

The PFD which is sensitive to the rising edge detects any phase or frequency difference between the input clock (fref) and the divided output clock (feedback) and generates a control signal proportional to the phase difference. The output signals up and down cause the charge pump to modulate the amount of charge in the low pass filter (VTOI) for the integral part (iint) and to feed current into the CCO for the proportional part (iprop). With these two currents and the DAC output irough the CCO is controlled. If feedback is leading fref, the oscillator is too fast. The down signal is activated and the CP subtracts some current iprop. When fref is in phase with the feedback the PLL will hold the control current at that level and phase lock will be achieved. Thus through this negative feedback arrangement, the PLL causes the feedback and fref signals to be equal with minimum phase offset. If the analog PLL becomes unstable, a signal pliko is generated which resets the digital PLL.

# **Architectural Description**

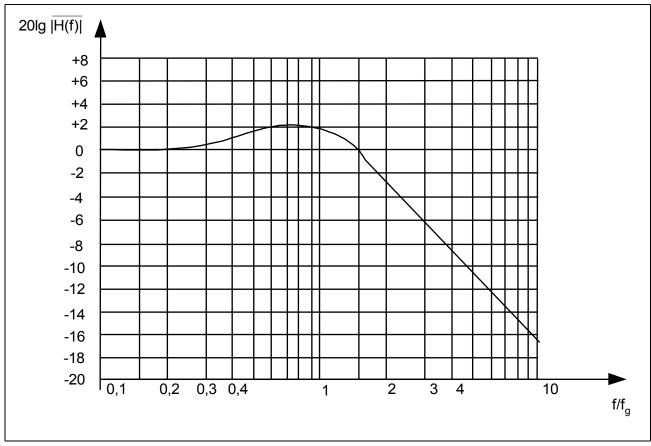

### 3.4.2.2 Jitter Transfer Function

Jitter transfers or jitter attenuation refers to the magnitude of jitter at the output of a device for a given amount of jitter at the input of the device. Input jitter is applied at various amplitudes and frequencies, and output jitter is measured with various filters depending on the applicable standards.

**Figure 8** shows the jitter transfer function of the SWITI device. The cutoff frequency of the integrated low pass filter is  $f_q = 15 \text{ kHz}$ .

Figure 8 APLL - Jitter Transfer Function

# **Architectural Description**

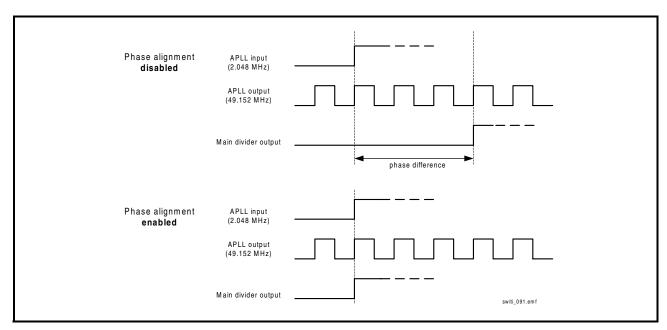

# 3.4.3 Phase Alignment

If the phase alignment function is enabled all PLL output signal and the main divider are edge synchronized with the PLL clock input. If the selected reference signal is less than 2.048 MHz the edge synchronization resolution depends on the selected external crystal/oscillator frequency. If the phase alignment function is disabled the PLL output frequency (49.152 MHz) is edge synchronized with the PLL input frequency and the main divider output frequencies are edge synchronized with PLL output frequency.

An example of phase alignment functionality is shown in Figure 9.

Phase alignment is required to keep the output signals in phase relative to the input signals. After reset phase alignment is automatically activated in slave mode and turned off in master mode.

Note: The phase alignment should be disabled for all reference frequencies < 2.048 MHz.

Figure 9 Example of Phase Alignment

# **Architectural Description**

# 3.4.4 PLL Synchronization

The PLL reference source can be selected from the primary reference master source (PFS, PDC, NTWK\_1/\_2). If the selected reference signal is less than 2.048 MHz the main digital PLL is used to synchronize the analog PLL. The digital PLL is sourced from the external oscillator, or crystal. In this case the analog PLL output frequency tolerance is equal to the external oscillator/crystal frequency tolerance.

Furthermore the analog PLL can be sourced directly from the external oscillator, or crystal, or from the PDC input. All generated output frequencies will have the same tolerance as the selected input frequency.

# 3.5 Loops

The loop command in the configuration command register **CMD2** provides support for automatic PCM-PCM loops.

All input lines are pad connected with the corresponding output line.

After the loop disable command was set the lines will be set in high-impedance after approximately two frames.

# 3.6 Read SWITI Configuration with Indirect Register Addressing

Since the SWITI configuration can be programmed with defined instructions in the CMD1 and CMD2 registers it is possible to read the current configuration through the indirect access registers. The indirect addressing is started by writing one of the five read configuration commands in the CMD2 register. The five commands can be separated in two groups, internal configuration and external line configuration. The internal configuration, e.g. clock generator, IREQ pin can be read with the command "Read Configuration". The internal settings are decoded with the instruction bits I3..0. The data rate for the PCM interface can be read with the "Read Local Bus (PCM) Line Configuration" command. The "Read GPCLK Configuration" and "Read Bit/Clock Shift Configuration" must be issued to get the GPCLK line configuration and the bit shift value. The TSV and CON registers contain the required information after the internal read process is complete. The recovery time is 240 ns. To read the correct configuration data from the TSV register it is not allowed to use the command "Read Time-Slot Value" before the TSV register has been read.

### **Architectural Description**

### 3.7 Power-On and Reset Behavior

### 3.7.1 Hardware Reset

There are two independent low active reset pins: RESET and TRST.

If the RESET pin is activated, it immediately sets all outputs and I/O ports into tri-state, except the ECLKO pin. After the reset process the correct external frequency must be set with the command 'Set external frequency' accordingly. This command starts the configuration process for the APLL. The APLL is locked after 750 µs. During this period the APLL is bypassed and the internal frequency is 2.048 MHz. If the APLL is locked the internal frequency will be 49.152 MHz.

Individual output sections must be enabled by setting the command in the configuration command register CMD1, or CMD2. Internally all state machines, counters and registers are cleared and set to their defined reset value.

The RESET pin doesn't control the boundary scan register and TAP-controller. If the TRST pin is asserted the TAP-controller will go into the Test-Logic-Reset state and all boundary scan elements are bypassed. All outputs and I/O-pins are controlled by the core logic and are tristated according to the programmed functionality or the core reset condition (pin RESET).

The hardware reset must be issued for a minimum of 1 µs, for more details please refer to the chapter "Hardware Reset Timing" on page 112.

#### 3.7.2 Software Reset

The software reset is accomplished by setting the 'Set Software Reset' command in the CMD2 register. The software reset clears the complete device except the clocking unit and the temporary microprocessor registers (e.g. CMD1).

The software reset can be deactivated with the 'Set Software Reset' command. During the software reset the microprocessor interface doesn't accept any other commands for a minimum of 1 µs.

**Description of Interfaces**

# 4 Description of Interfaces

### 4.1 Local Bus Interface (PCM)

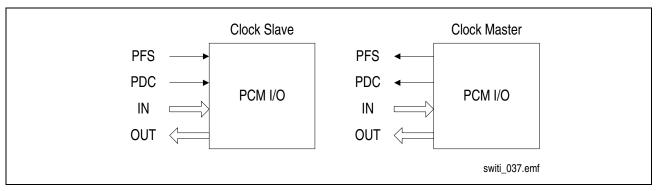

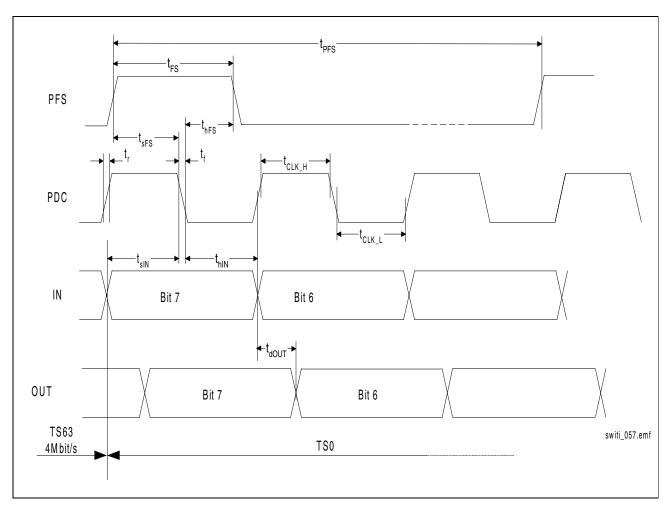

The local bus is a PCM interface consisting of input and output data lines (IN, OUT), a PCM data clock PDC and a frame synchronization signal PFS.

Figure 10 PCM Interface Configurations

The **PFS Frame Sync** is a 8 kHz signal and delimiting the frame. This input signal is used by the SWITI to determine the start of a frame. A frame is divided into 8-bit wide time-slots. The amount of time-slots within a frame depends on the selected data rate of PDC which can be 2.048 Mbit/s, 4.096 Mbit/s, 8.192 Mbit/s, 16.384 Mbit/s. The PFS input has a Schmitt-Trigger characteristic.

The **PDC Data Clock** input supplies the SWITI with a data clock. It can be operated with 2.048 MHz, 4.096 MHz, 8.192 MHz, or 16.384 MHz data rate clock depending on the selected **highest** data mode. The PDC clock signal must be equal or higher as the highest data rate. The PDC input has a Schmitt-Trigger characteristic.

A clock slave **must receive** PFS and PDC whereas a clock master **drives** these signals. To enable or disable the signals for the clock master the command 'PCM Clock Input/ Output Selection' must be issued.

The time-slots are transmitted and received via 16 input and 16 output lines (IN[15:0], OUT[15:0]). The input lines have a Schmitt-Trigger characteristic. The output lines have tristate outputs with push-pull characteristic. For every time-slot not participating to a connection the output is high impedance.

With the special command "Local Bus (PCM) Standby" in the CMD2 register it is possible to set all PCM lines in a high impedance state during the normal operation mode. All PCM lines are in high impedance state after the reset process and must be enabled with the "Local Bus (PCM) Standby" command. All lines which are not participating on a switching operation are in high impedance state and the time-slot information on the input lines are discarded automatically.

### **Description of Interfaces**

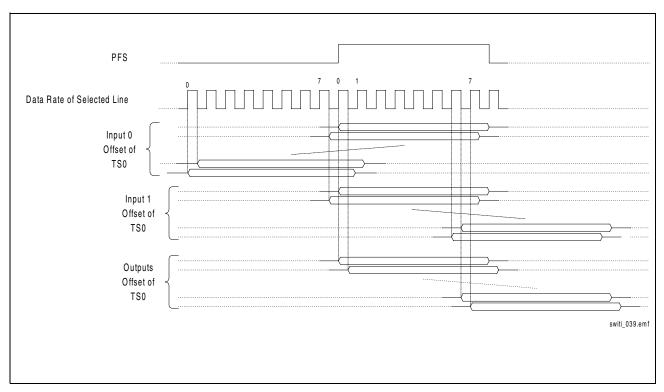

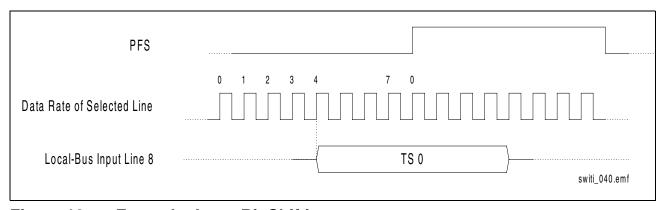

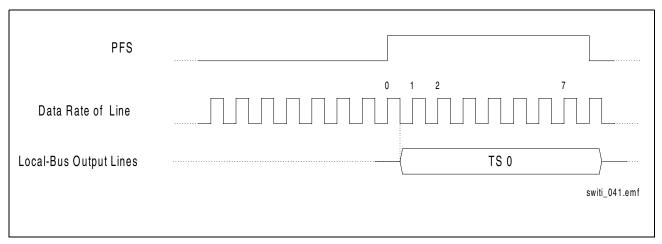

Figure 11 PCM Bit Shifting

For **each** PCM input line the offset of time-slot zero can be adjusted in a range from 0 to 7 bit in half clock resolution before or after the PFS rising edge. For **all** output lines the offset of time-slot zero can be adjusted in a range from 0 to 7 bit in half clock resolution after the PFS rising edge.

The resolution depends on the selected data rate that means the resolution doesn't depend on the PDC signal.

After the reset process the bit shift is disabled for all lines. That means the time-slot 0 starts with the rising edge of PFS. All input data will be sampled with falling edge of the selected data rate and the output data are valid with the rising edge of the selected data rate.

### 4.2 Data Rate

The MTSI provides the programming of different data rates for all data lines. All local bus lines can operate with 2.048 MHz, 4.096 MHz, 8.192 MHz, and 16.384 MHz having data rates of 2.048 Mbit/s, 4.096 Mbit/s, 8.192 Mbit/s and 16.384 Mbit/s.

The input and output lines are independent of each other, i.e. for a given bus line the input and the output lines can be programmed with different data rates.

The maximum aggregate data rate supported at the input and output bus lines is 262.144 Mbit/s, with all lines operating at 16.384 Mbit/s (i.e. 16 lines x 16.384 Mbit/s per line = 262.144 Mbit/s, as input and/or output).

### **Description of Interfaces**

# 4.3 Microprocessor Interface

A standard 8-bit multiplexed or non-multiplexed  $\mu P$  interface is provided. It is compatible to Intel/Siemens (e.g. 80386EX, C166) or Motorola (e.g. 68040, 68340, 68360, 801) bus systems. If the GPIO port is not needed it can be used to provide a 16-bit  $\mu P$  interface. The 16-bit mode is determined according to MODE16 input pin.

MODE16 = '0' -> 8-bit interface

MODE16 = '1' -> 16-bit interface

This chapter describes how to configure the µP interface to each mode.

### 4.3.1 Intel/Siemens or Motorola Mode

The Intel/Siemens or Motorola mode for the  $\mu P$  interface can be configured during the hardware reset process in conjunction with the ALE pin.

- ALE permanently driven to 'low' => Motorola mode

- ALE permanently driven to 'high' => Intel/Siemens mode

- Edge on ALE => Intel/Siemens multiplexed mode

A falling or rising edge on ALE during the normal operation selects the multiplexed mode immediately. With the hardware reset and the tied ALE pin it is possible to return to the Motorola or Intel/Siemens mode.

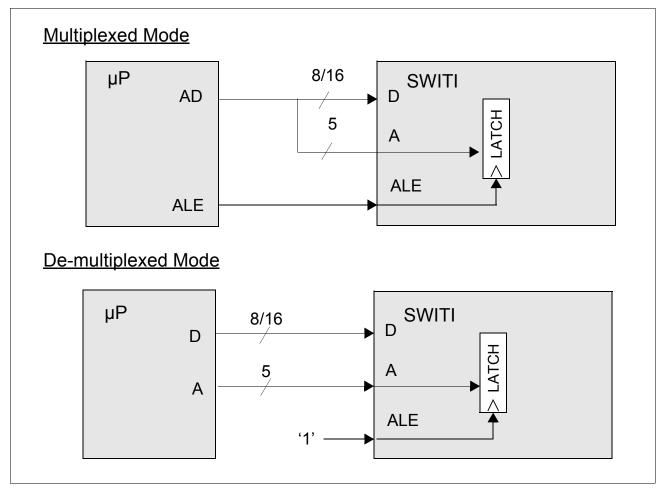

# 4.3.2 De-multiplexed or Multiplexed Mode

In both modes, the A-bus and the D-bus are used in parallel. The A-bus should be connected to the LSBs of AD-bus, coming from the  $\mu$ P, also in multiplexed mode.

The next figure describes the connection to the address and data buses in the different modes.

Note: Motorola mode is used only with de-multiplexed AD bus. Intel/Siemens mode may be used with both, multiplexed or de-multiplexed AD bus.

# **Description of Interfaces**

Figure 12 Multiplexed and in De-multiplexed Bus Mode

Note: In both modes only the 5 LSBs of A-bus or AD/bus are connected to the Address inputs.

### **Description of Interfaces**

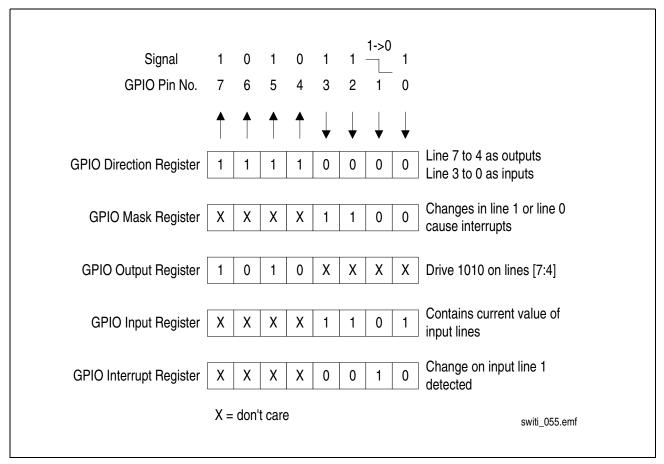

# 4.4 General Purpose Port (GPIO)

This port consists of 8 lines each one configurable as input or output. A change on an input line may cause an interrupt (if not masked). The user has access to the port configuration and information via the appropriate registers of the  $\mu P$  interface.

Figure 13 shows an example.

Figure 13 GPIO Port Configuration Example

# 4.5 General Purpose Clocks

The SWITI provides 8 general purpose clock lines. With two independent commands in the CMD2 register the lines can be configured as frame group signals or individual clock signals. The last written command for a line is valid and controls the multiplexer.

### **Description of Interfaces**

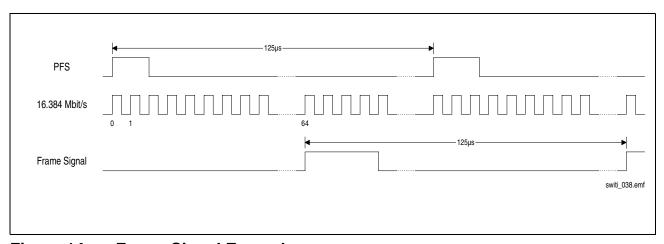

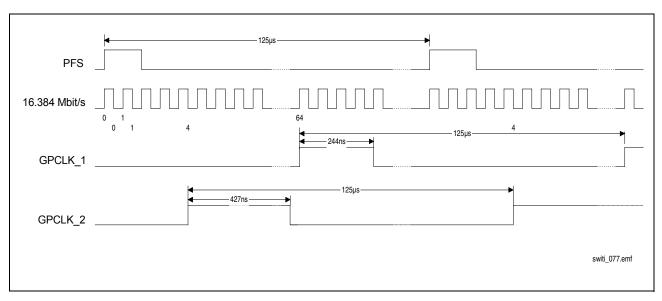

# 4.5.1 Frame Group Outputs

Via 8 output lines it is possible to provide 8 different framing signals which are used for synchronization purpose. All signals have a period of 125 µs. Their offset can be programmed individually within the PFS determined frame in a resolution of 61 ns (i.e. 1/16.384 MHz). The default start point for the offset is the beginning of a frame (rising edge of PFS and the clock signal). The start point for the offset can be shifted for an half clock cycle, that means the second start point is determined with the rising edge of PFS and the next falling edge of the clock signal (as shown in **Figure 14**). The high time of the signal can also be programmed in steps of 61 ns. All frame signals can be controlled as high or low active.

Figure 14 Frame Signal Example

Figure 14 shows an example of a frame signal beginning with the rising edge of the 64th clock cycle with a length of 4 clock cycles. Further programming examples can be found in **Chapter 6.8.1**.

# 4.5.2 GPCLK as Clock Outputs

All 8 GPCLK lines can be configured as individual clock outputs with 8 kHz, 2.048 MHz, 4.096 MHz, 8.192 MHz, 16.384 MHz and for test purposes with the internal frequency or the input frequency of the analog PLL (APLL). All clock signals are generated from the analog PLL output frequency which is the internal frequency. The quality of all output frequency signals depends on the quality of the selected input PLL frequency.

### **Description of Interfaces**

# 4.6 JTAG (Boundary Scan)

The SWITI provides a fully IEEE 1149.1 compatible boundary scan support consisting of:

- a complete boundary scan chain

- a Test Access Port controller (TAP controller)

- five dedicated pins: TCK, TMS, TDI, TDO and a TRST to asynchronously reset the TAP controller

- one 32-bit IDCODE register

# 4.6.1 Boundary Scan

All pins except power supply and crystal are included in the boundary scan. Depending on the pin functionality one (input), two (output, enable) or three (input, output, enable) boundary scan cells are provided.

The maximum clock rate at pin TCK is 10 MHz.

# 4.6.2 Test-Access-Port (TAP)

The following signal pins allow the boundary scan test logic to be accessed:

- TCK

- Test Clock input to which a central BSc test clock is applied. This BSc test clock is independent of the system clock. Clock phases are derived from this clock for test sequence control.

- TMS

- Test Mode Select control input for which the desired status changes at the TAP controller by applying a certain level (0/1) caused by the rising edge of TCK.

- TDI

- Test Data Input whose data is inserted into the test logic with the rising edge of the TCK.

- TDO

- Test Data Output with tristate capability which is only active during the SHIFT-IR and SHIFT-DR controller state, and whose data is driven with the falling edge of TCK.

### **Description of Interfaces**

### 4.6.3 TAP Controller

The Test Access Port (TAP) controller implements the state machine defined in the JTAG standard IEEE 1149.1.

Transitions on the pin TMS cause the TAP controller to perform a state change. The possible instructions are listed in the following table.

Table 9 TAP Controller Instructions

| Code | Instruction    | Function                                          |

|------|----------------|---------------------------------------------------|

| 0000 | EXTEST         | External testing                                  |

| 0001 | IDCODE         | Reading ID code                                   |

| 0100 | HIGHZ          | High impedance state of all boundary scan outputs |

| 0101 | SAMPLE/PRELOAD | Snap-shot testing                                 |

| 0110 | INTEST         | Internal testing                                  |

| 0111 | CLAMP          | Reading outputs                                   |

| 1111 | BYPASS         | Bypass operation                                  |

The instruction length is four bit.

**EXTEST** is used to verify the board interconnections.

When the TAP controller is in the state "update DR", all output pins are updated with the falling edge of TCK. When it has entered state "capture DR" the levels of all input pins are latched with the rising edge of TCK. The in/out shifting of the scan vectors is typically done using the instruction SAMPLE/PRELOAD.

### **INTEST** supports internal chip testing.

When the TAP controller is in the state "update DR", all inputs are updated internally with the falling edge of TCK. When it has entered state "capture DR" the levels of all outputs are latched with the rising edge of TCK. The in/out shifting of the scan vectors is typically done using the instruction SAMPLE/PRELOAD.

#### SAMPLE/PRELOAD

The SAMPLE/PRELOAD instruction enables all signal pins (inputs and outputs) to be sampled during operation (SAMPLE) and the result to be shifted out through the shift BSc register. The function of the internal logic is not influenced by this instruction. While shifting out, the BSc cells can be serially loaded at the same time with defined values through TDI (PRELOAD). The SAMPLE/PRELOAD instruction selects the boundary scan register in normal mode. In state CAPTURE-DR data is loaded into the boundary scan register with the rising edge of TCK. In state UPDATE-DR the contents of the boundary scan register are written into the second register stage of the boundary scan

### **Description of Interfaces**

register. This data become effective at the outputs only if an instruction has been activated that sets the BSc register to test mode: e.g. EXTEST or CLAMP.

#### **IDCODE**

The 32-bit identification register is serially read out via TDO. It contains the version number (4 bits), the device code (16 bits) and the manufacturer code (11 bits). The LSB is fixed to '1'...

| Version Device Code |                     | Manufacturer Code |   | Output |

|---------------------|---------------------|-------------------|---|--------|